Hi All,

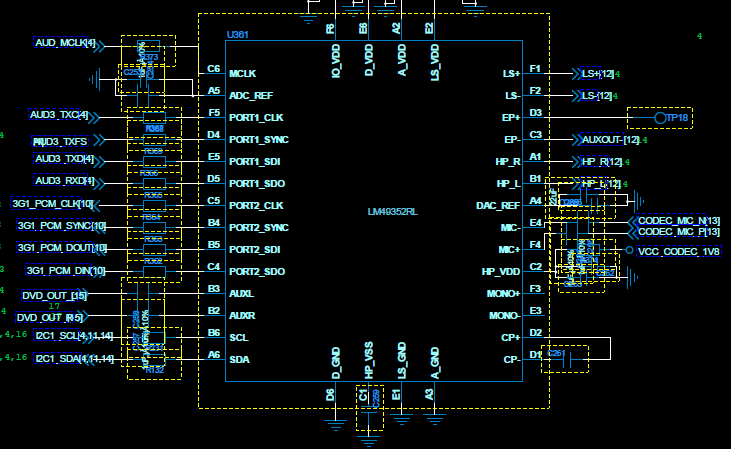

We are using LM49352 in our project for following config.

Port 1 -> for I2S playback with LM49352 as clock & sync master

Port 2 -> for PCM for 3g Audio call with LM49352 as Slave

We have finally brought up basic things but still we have the following issues

1. Left channel audio is not working in I2S mode

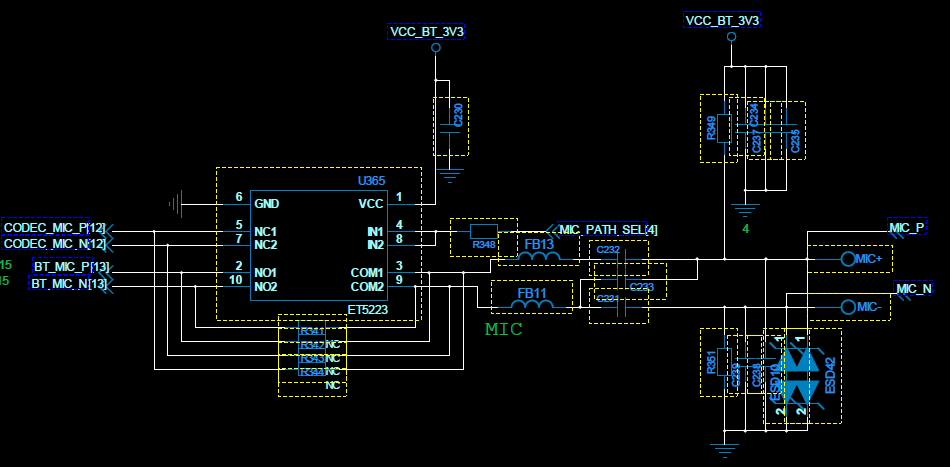

2. Heavy noise in 3G voice call.

We are totally stuck here. Since we are not getting the support from respective FAE also.

We are in the crucial stage of project completion.

Can anyone help us to sort out the issue.

Your help will be highly appreciated !!!

Thanks and Regards

Sriram.