Hello,

One important thing to understand and to setup when are going to used 32XX families for the first time is

how to get a correct clock scheme for the device.

I think there is a lack of description on the relationship (when miniDSP's are planned to be used) between clocks setup and miniDSP cycles...

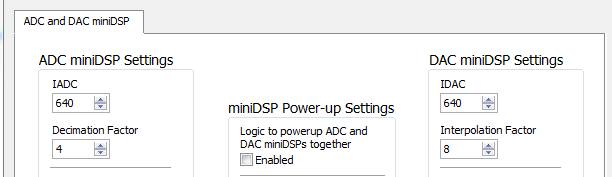

Can someone explain or point me out on a document if there is one on the relationship between IDAC/IADC setup and DSP_A DSP_D cycles.

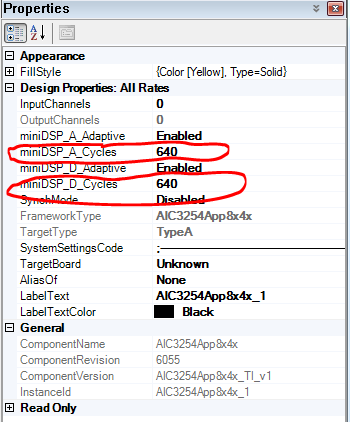

My first DSP trials (just a DIN/DOUT digital loopback) fails to run and it takes me a while before to understand that my DSP cycles i.e 904 (default 3254_8x4 framework values when you dump the block on your scheme) were greater than the acceptable values for my design and my actual clock setup.

The clock setup and pll setup is widely documented on the 3254 spec but there absolutely nothing about the relationship with miniDSP's capabilities.

If there is a document explaining this so far it must referenced in clock setup section of the main 3254 specification. IADC and IDAC are undefined acronyms ...

Let me know. Thanks.