Dear TI,

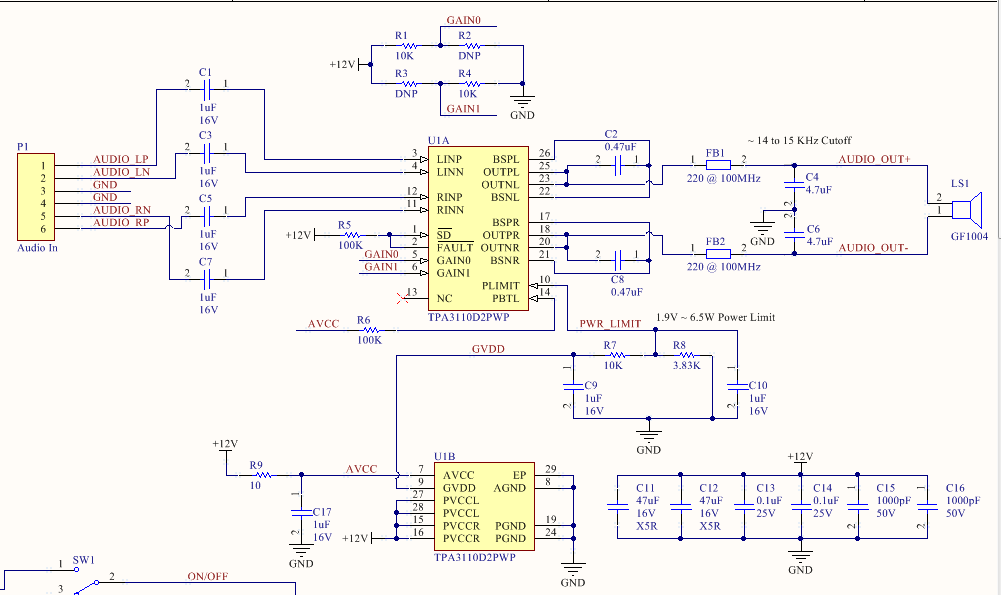

I have the design below and on power up (no input applied to any speaker audio input channels) the #FAULT Pin pulls low, cycles back to 2V, pulls low again, etc. (BTW produces a series of low frequency click sounds on the speaker output at the same frequency as the shutdown fault cycle).

What would cause this ? Also occurs when I take the speaker off completely.

Is the GAIN0 and GAIN1 settings too high ? Also the PWR_LIMIT Voltage is 1.9V for a 6.5W limit and AVCC and GVDD all look clean and stable.

I checked with the PCB assembly house and they indicated that they made sure that the PGND pads for the heatsink were all properly attached etc.

I checked the temperature of the device and it is around room temperature so there is no thermal issue.