Good day,

I'm using a kl16 cortex m0 MCU from Freescale together with an TAS2505. The audio data is streamed via I2S to the TAS2505 and the configuration data via I2C.

I was following the 4.0.7 Example Register Setup to Play Digital Data Through DAC and Headphone/Speaker Outputs in the slau472.pdf. I can hear some audio coming out of the speaker, but very distorted and not at all like it is supposed to be.

Anyone has a similar experience?

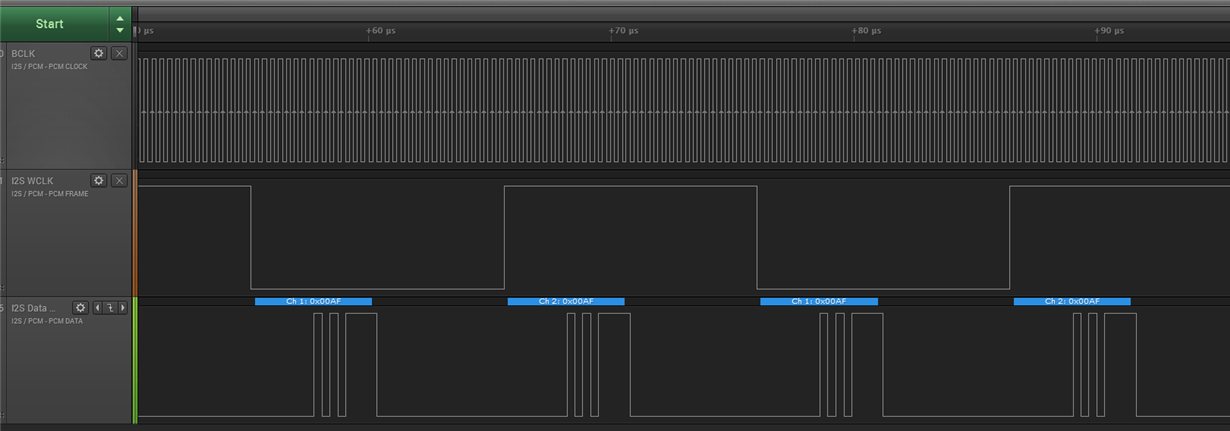

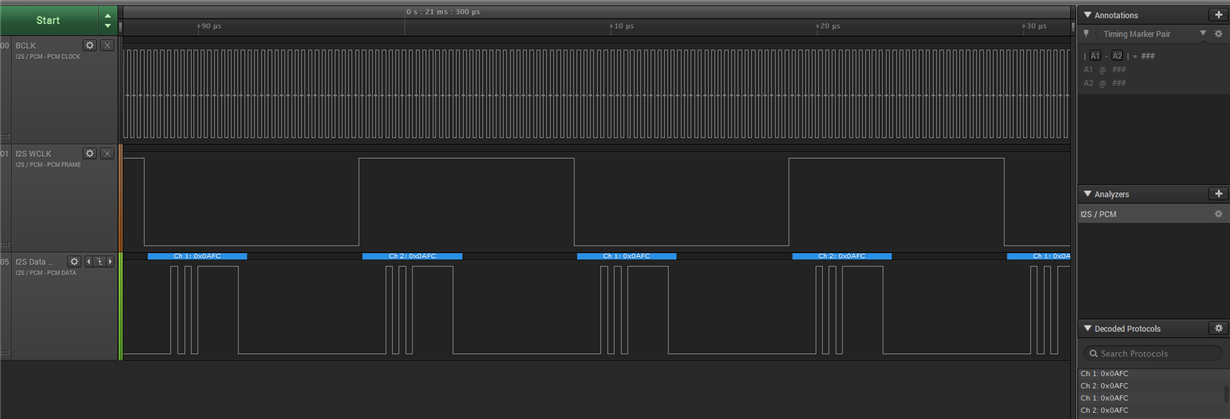

My setup: using digital input with I2S, MCLK from an external source, WCLK and BCLK provided by the TAS2505. WCLK = 44.1 kHz, BCLK = 1.4MHz. 16bit words, 2 word per frame.

Any help or ideas are appreciated.

Regards

Roland