Hello,

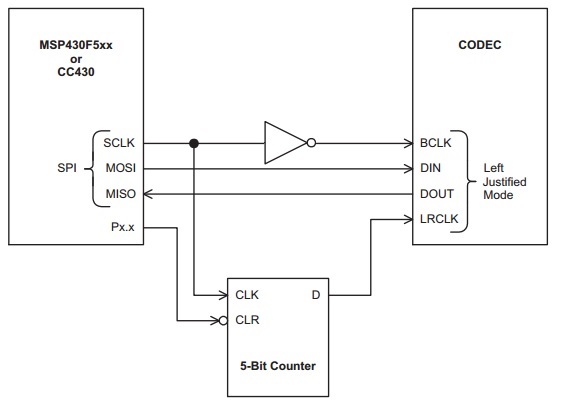

As I've posted before, we've implemented a new hardware design that uses the TLV320AIC34 connected to an MSP430F5359 using the connections described in app note is based on the appnote SLAA449A. We're running the MSP430 at 20MHz and supplying that 20MHz clock to the Codec's MCLK_A & MCLK_B inputs. I'm attempting to sample a signal around the 20Khz range in this example. Here is my Codec Configuration sequence:

Start by resetting the Codec A & B.

Delay 5 microseconds

Release reset on Codec A & B.

Delay 10 microseconds

Set the following Registers to Configure

Data stream and clock configuration:

Register Addr = Value

Register 7 (0x07) = 0x80

Register 9 (0x09) = 0xC0

Register 3 (0x03) = 0x21

Register 2 (0x02) = 0x22

Set Differential Input Register Configuration:

// Left Channel Config CodecA & B

Register Addr = Value

Register 7 (0x07) = 0x8A

Register 43 (0x2B) = 0x00

Register 37 (0x25) = 0xC0

Register 82 (0x52) = 0x80

Register 86 (0x56) = 0x09

Register 40 (0x28) = 0x40

// Right Channel Config CodecA & B

Register Addr = Value

Register 7 (0x07) = 0x8A

Register 44 (0x2C) = 0x00

Register 37 (0x25) = 0xC0

Register 92 (0x5C) = 0x80

Register 93 (0x5D) = 0x09

Register 40 (0x28) = 0x40

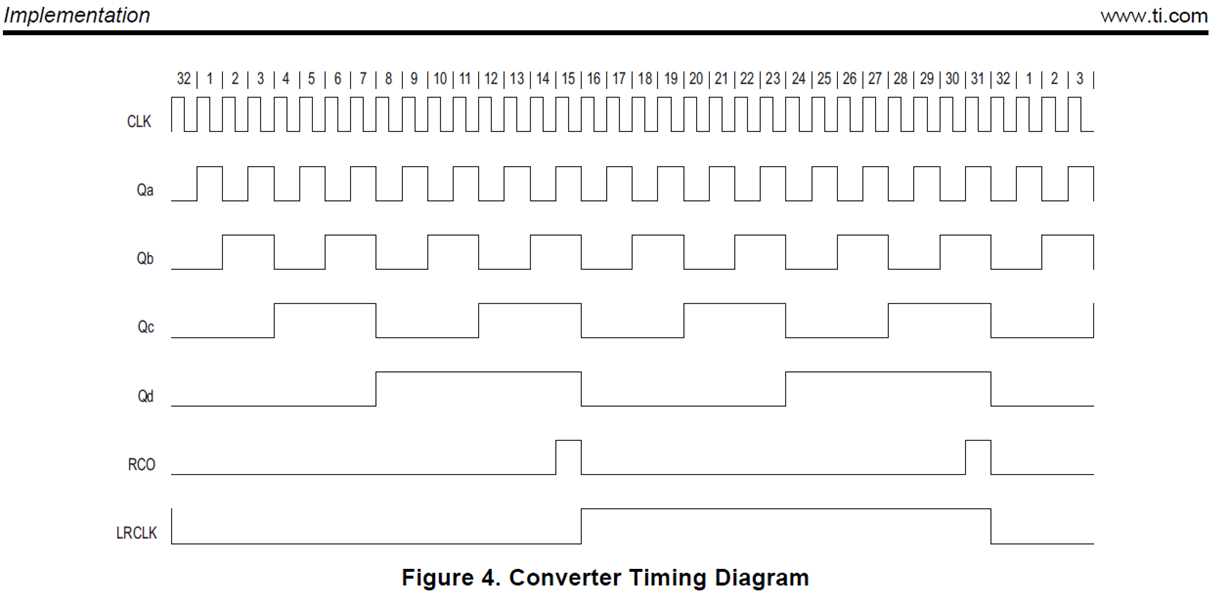

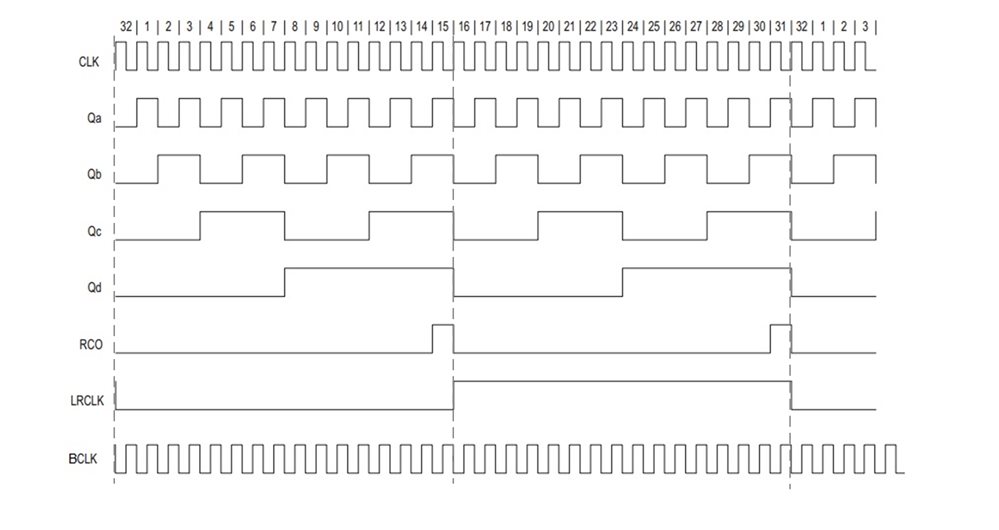

I have previously configured the SPI interface to use a bit rate divider of 0x1F which should yield a real divider of 0x20, or 32. My input clock to the SPI peripheral should be the SMCLK for the micro which is the same clock being fed to the codec's MCLK. This clock should be set at something close to 20Mhz. So, my bit rate on the SPI interface should be 20Mhz / 32 = 625Khz.

So, the "sampling frequency", or the frequency that I should be reading samples out of the codec should be 625khz / 32 bits = 19531.25.

The corresponding setting based on my codec configuration should be setting fsref as 20Mhz / (128/Q) where Q = 4 which yields a value of 39062.5. I then have the ADC/DAC sampling set to fs/2 which yields the final sampling frequency of 19531.25 which should be an EXACT match to my SPI sampling frequency. Especially when we consider that both the codec and my SPI port are clocked with the same 20Mhz clock source. Things should be synchronized.

However, in my input data stream that I read from the codec, I can see "flat spots" in my input sine wave periodically occurring once every 32 samples. I have no explanation for this. My SPI ports are all DMA driven so interrupt latency should not be an issue. By DMA sample size is currently set to 64 samples, so even that doesn't correspond to the precise 32 sample flat spots. It sure looks like I'm getting out of sync with the codec somehow, but I cannot see where this could be happening.

Attached is an excel spreadsheet showing the data sampled from the codec. I have some initial startup sync issues in my buffer, so the first 60 or so samples should be ignored. However, following that, you can clearly see how the flat spots occur regularly at 32 sample intervals.