Hello

My customer is using PCM5102A for their production.

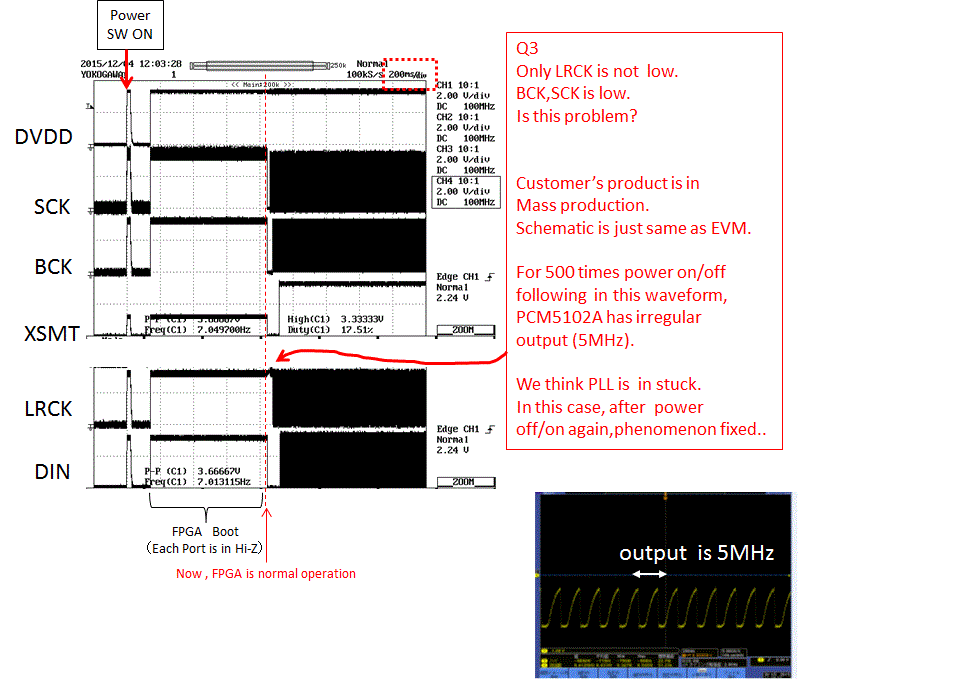

I2S signal coming from FPGA (GPIO), in front of PCM5102A.

Now they are in trouble such a ' no sound ' occasionary. ( 1time / 300times power off/on )

' no sound ' means 5MHz irreguar output , it seems PLL is in stuck.

Would you please give us advice as soon as possible? ( WE need your answer within 12 hours..)

Customer is stooping their mass production line now.

Q1 Please adivse about customer's start up waveform for I2S input... Please see attached.

Q2 How long is internal reset period ( in msec ) Page 10 Fig 11 of PCM5102A d/s?

Q3 In the internal reset period, all of I2S clocks (LRCK/BCK/SCK) should be low? Or valid clock?

( Customer is setting Hi-Z in the internal reset period , and then SCK=L/BCK=L/LRCK=H)

Please advise how customer should be set the I2S clocks in the power on.

I am so sorry but I hope your answer within 12hours. ...

Please allow me such a urgent inquiry,,, but please help us.

WITH MY BEST REGARDS