Hello

Would please let me know about PCM1863?

Customer is using PCM1863 for DVDD=IOVDD=1.8V as I2S salve mode.

Q1

Please let me confirm.

Can we use PCM1863 at DVDD=1.8V?

We see Data sheet page 6 "6.5 Electrical Characteristics, DC" shows several 1.8V DVDD current specs,...

however,data sheet p60/Table 24 describes DVDD should be 3.3V.

Which is correct ? ( Page 6 is TYPO of IOVDD, not DVDD...? Or description on page 60 is not enough??)

Q2

If customer use PCM1863 for AVDD=3.3V,DVDD=IOVDD=1.8V, customer should do following 3 things.., isn't it?

Please let me confirm

a;Input 1.8V to LDO pin.

b;set PCM1863 slave mode via SPI/I2C. Page.0 0x20 - Set MST_MODE=1 (I2S Slave)

c;PLL is disabled Page0/0x20 via SPI/I2C

Page0 / Register 32 (Hex 0x20) b0 (CLKDET_EN)=0 Page0 / Register 40 (Hex 0x28) b0 (PLL_EN)=0

Q3

If customer used PCM1863 for Slave mode , i.e. customer do not use PLL,

he should apply SCK,BCLK,LRCK from external circuit.

In this slave mode , he should keep following? ..

a:BCK per LRCK should be set to 64.

b:Keep the 8.21.5.1 Interface Timing

c:Master clock(SCK) should be audio clock, for ex. 256 or 384 or 512fs

d:Master clock( =sck = OSC clock on page 62 )should be correctly applied at the same time of DVDD exceeds > 1.5V for digital reset.

Q4

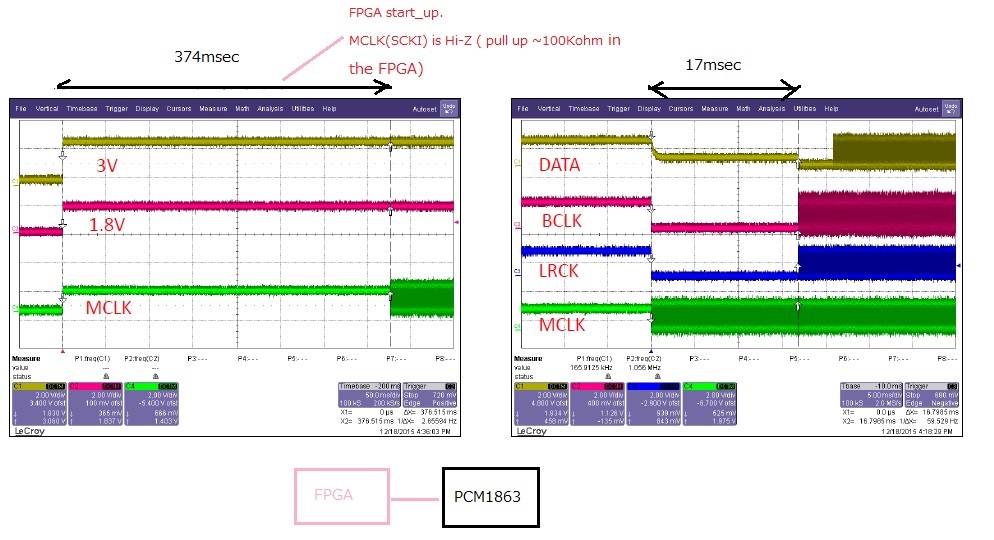

In customer's product, they don't keep the criteria on Q3-d ( please see attached ).

As per customer's comment, 1time /20times power on test , frequency responce is illegal

( Drops in a few KHz: BAD case/ 20KHz: Good case).

In such a case, PCM1863 stucks in such a phenomenon unless othewise Ower Off/ On again.

Following should be necessary?

* SCKI should be applied at the same time with DVDD >1.5V?

* Should customer apply LRCK/BCK at the same time of SCKI (OSC clock ) ?

Q5

Would you please let me know the way to digital reset the PCM1863 except power off/on?

There are no reset pin in PCM1863, so we can use page0/ REG 0x70 ?

Please advise.

Thank you for your cooperation and with my Best Regards