Hello.

I have TLV320AIC3204EVM-K development board.

The simple functions as recording and playback works good. But my goal is the next:

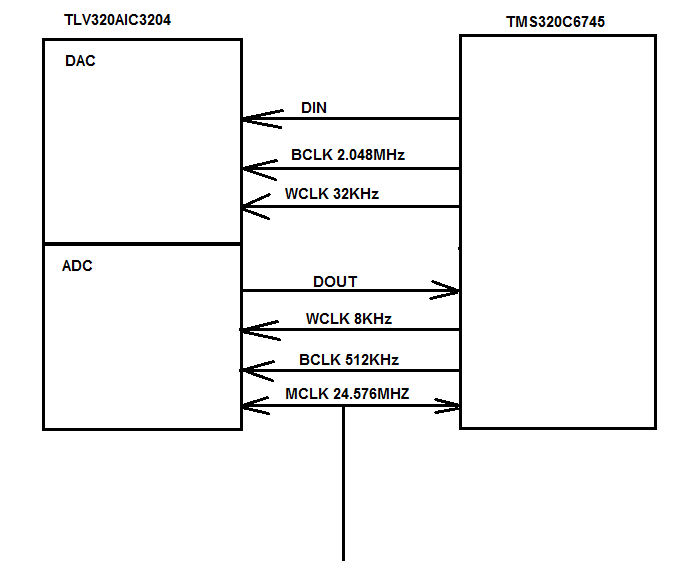

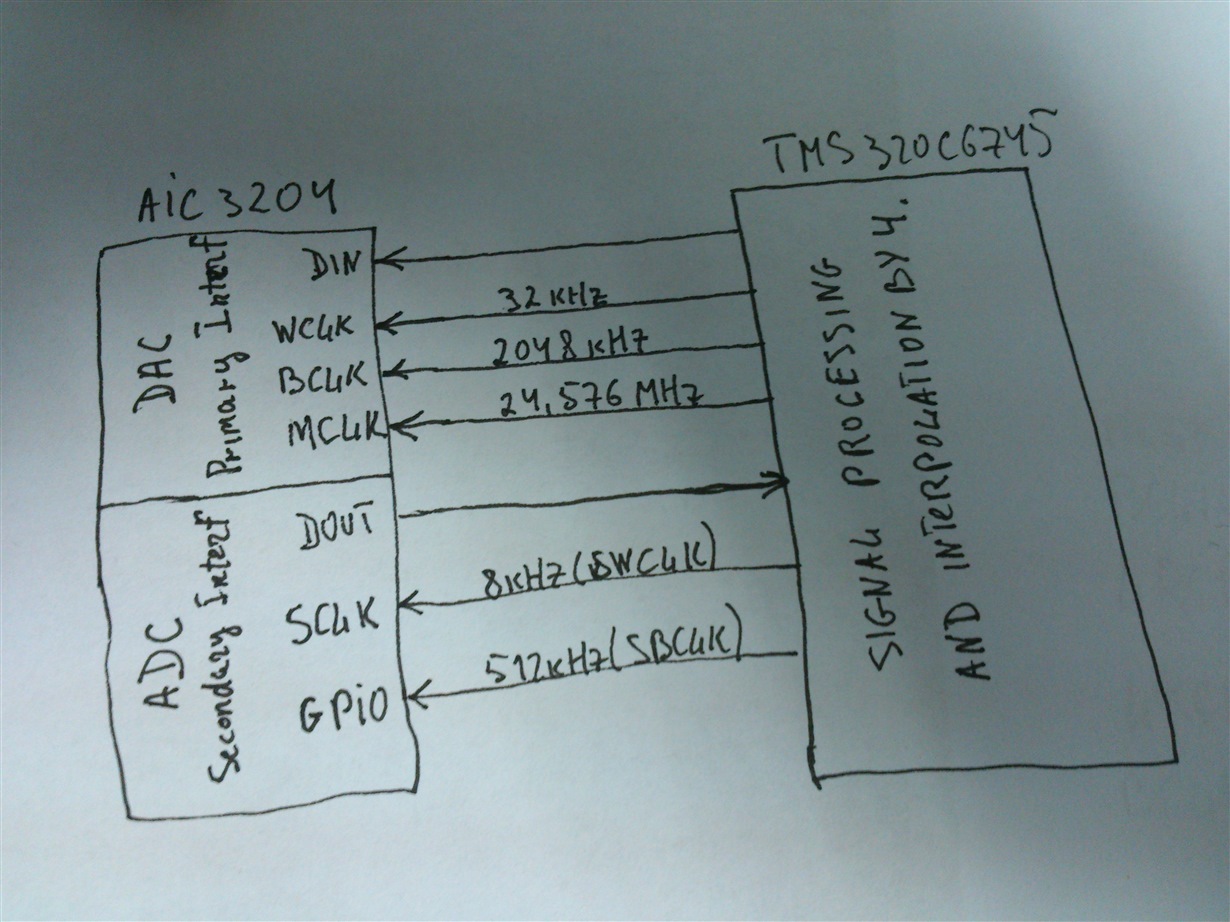

I want to use codec with ADC and DAC differ sampling rates. Codec must works in Slave mode.

I read slaa557 and slaa404c and find the next information:

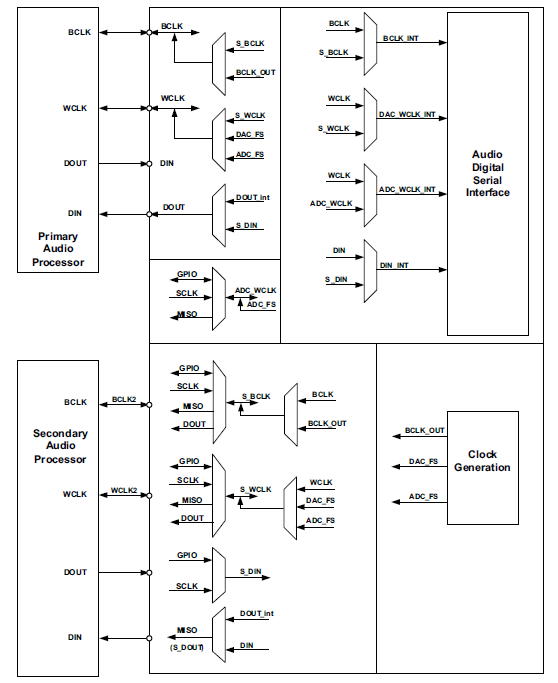

A typical audio interface bus consists of four signals: the word clock, bit clock, data in (DAC data) and

data out (ADC data). The AIC32x4 has two audio buses, where the primary bus has its signals fixed to the

WCLK, BCLK, DIN, and DOUT pins and the secondary bus and ADC word clock can be routed to

multifunction pins. The ADC word clock (ADC_WCLK) is suitable for cases where the ADC and DAC

sampling rates differ. The audio bus signals can either be supplied by an external processor or generated

by the AIC32x4.

The next picture is shocked me.

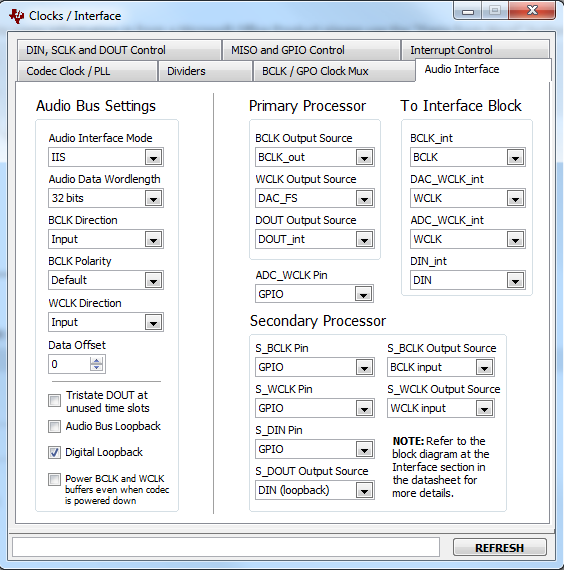

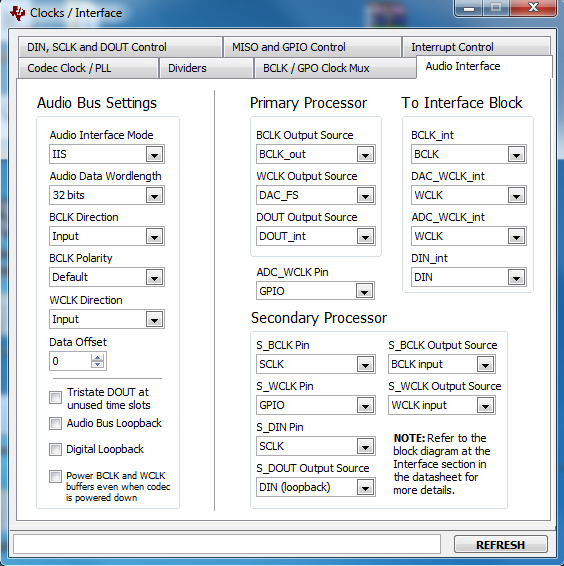

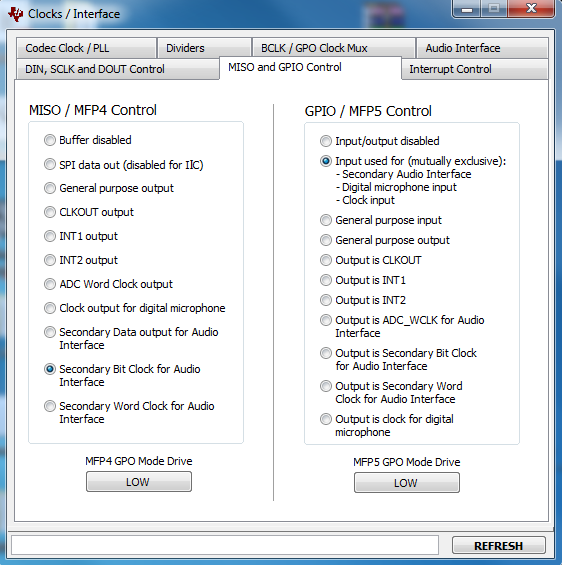

Can anybody give me a simple explanation how works and what is needed secondary I2S.

What settings I must use for my schematic diagram.

I am hope for your understanding.

Thanks.