Hi,

I am trying to make TAS5760M DAC amplifier work properly, but the are some problems I have to face and I would like community's help.

I have make my own PCB layout on a prototype version using the software mode and the I2C slave address of the TAS is routed to ground via a pull down.

While I have perfect communication with the TAS5760 through the I2C protocol(I can read and write registers), and while I have set the I2S protocol perfectly(working perfect on DS7212 codec of Dialog) I am not able to get sound through the TAS5760M that I would like to use on our production line.

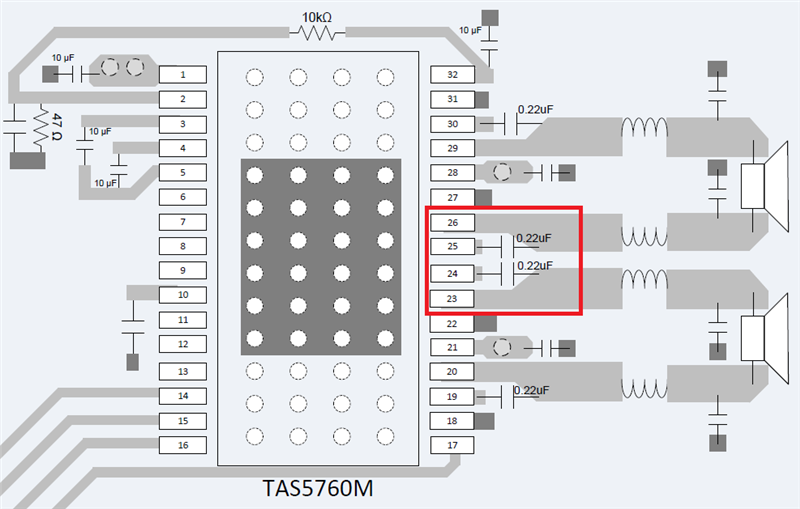

Actually the Stereo BTL Using Software Control, 32-Pin DAP Package Option Typical Application on reference manual have some misunderstood thing.

According the above steps of startup sequence there are some misunderstood to me:

2) The !SPK_SD pin is active low, that means that the host MCU must provide the pin with logic HIGH as idle state, BUT how this could be happen as there is no power supply yet. Power supply is going to be aplied to the system on the next step(STEP 3).

4) Typical I2S host mcu protocol can only apply the SCLK and LRCK signals only if there is an ongoing playback, So how could I start 3 signals together(MCLK,SCLK,LRCK) without configured the control port first according the audio playback requirements, which is configured on the next step(STEP 5) according the steps above.

Except these I have some additional question to do:

1) There is a note that told me to bring the !SPK_SD pin LOW in order to make changes on control port via I2C, BUT that means that I have to ShutDown the playback in order to volume up for example??

2)If I am not wrong there is a reference that informs me that, toggle !SPK_SD pin is needed in order to sense the possible problem may has occur on the amplifier part of the ic, BUT according the !SPK_SD pin philosophy if I pull this pin LOW I have Shutdown state and If I pull this pin HIGH I got a non-Shutdown state, so maybe "" "Toggle" is not the right word.??

3)Is there any more spesific step by step tutorial on how to implement the Stereo BTL Using Software Control, 32-Pin DAP Package Option.

PS.:Firstly I got non-latching SPK_FAULT indication when there is no I2S data on TAS5760. After I2S data have been applied to the TAS (I mean SCLK,LRCK and DATA signals appears), i got latching SPK_FAULT indication.

Thank you in advance

Pelekis Marios