Hello

Would you please advise about PLL setting for PCM3070?

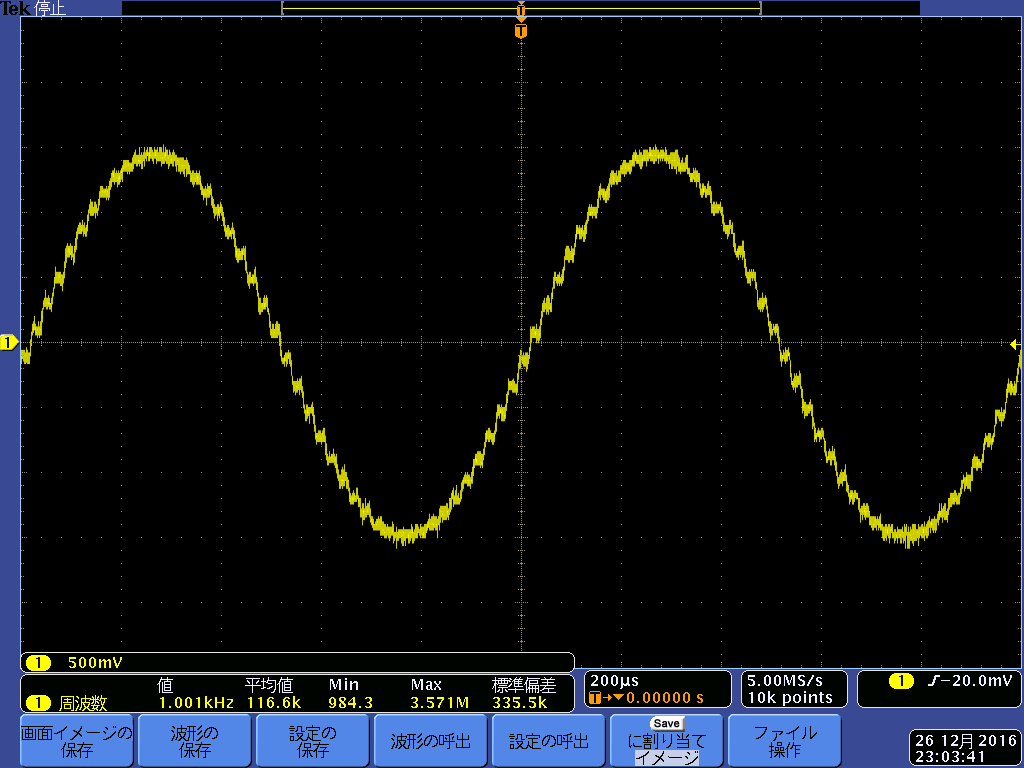

We have problem of THD= over 3% at customer's ES board when fs=44.1KHz it these

a couple of weeks. ( When fs= 192KHz, THD < 0.03% and seems OK )

Customer use PCM3070 as following way.

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

case1 input i2s data is fs=192KHz. I2S slave. MCLK is 24.576MHz from Wireless SoC,

case2 input i2s data is fs=44.1KHz. I2S slave. MCLK is 22.5792MHz from Wireless SoC

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

Therefore, customer and I think following setting is avilable for both case 1 and case2 because MCLK is set differently from SoC.

===

PLL_CLK_IN= 24.576 MHz Or 22.5792 MHz

P=2 ===> PLL_CLKIN/P < 10MHz~20MHz

J.D= 8.0

R=1

So, PLL_CLK= 98.3MHz=CODEC_CLK_IN

NADC=4 ==> DAC_miniDSP is 24.6MHz( <55.2MHz)

MADC=4 ==> DAC_MOD_CLK is 6.14MHz ( <6.2MHz )

AOSR =32

Therefore

DAC_fs = 192KHz Or 176.4 KHz

DVDD =1.8V ( > 1.65V )

===

I attach the .cfg file.

Question 1

What is PLL clock range High Or Low? ( Page 0 Reg 4 )

Does it mean Table 2-23 (DVDD >1.26V Or DVDD > 1.65V ) ?

Question 2

If I set DAC_FS as 176.4KHz , I2S data is available not only fs= 176.4KHz data but also

fs=44.1KHz data with no problem?

Also If I set DAC_FS as 192KHz, I2S data is available not only fs= 192KHz data but also

fs=48KHz data with no problem?

Question 3

I understand " DAC_FS" is sampling rate of DAC for incoming I2S data.

Application Reference Guide ** page 46 says.

2.8MHz < DOSR * DAC_FS < 6.2MHz

I just follow DOSR * DAC_FS for this criteria, no need to follow DOSR *input fs.

Is is correct?

Question 4

If I violate CODEC_CLKIN 137MHz ( Application Reference guide Table 2-23 )

when I set P=1 , what phenomenon may occur ?

Question 5

I appreciate if you have any advise the check point for improving THD.

I recommend customer that just send i2c address and register value by base_main_Rate_192.cfg file

from MCU.

But is there any lack for software implementation ?

I am sorry that I do not know how to use following well .....

base_main_Rate44_pps_driver.h

pps_driver.c

pps_driver.c

Thank you and with my Best Regards

**