We are using the PCM5101A as a Clock Slave mode with Master/System Clock (4 Wire I2S). The DAC process I2S signals with 48 Khz sampling rate and a data resolution of 16 bit per channel. The System clock input to the DAC (SCK) is a 18.432 Mhz 3.3V 25 PPM oscillator (384*fs).

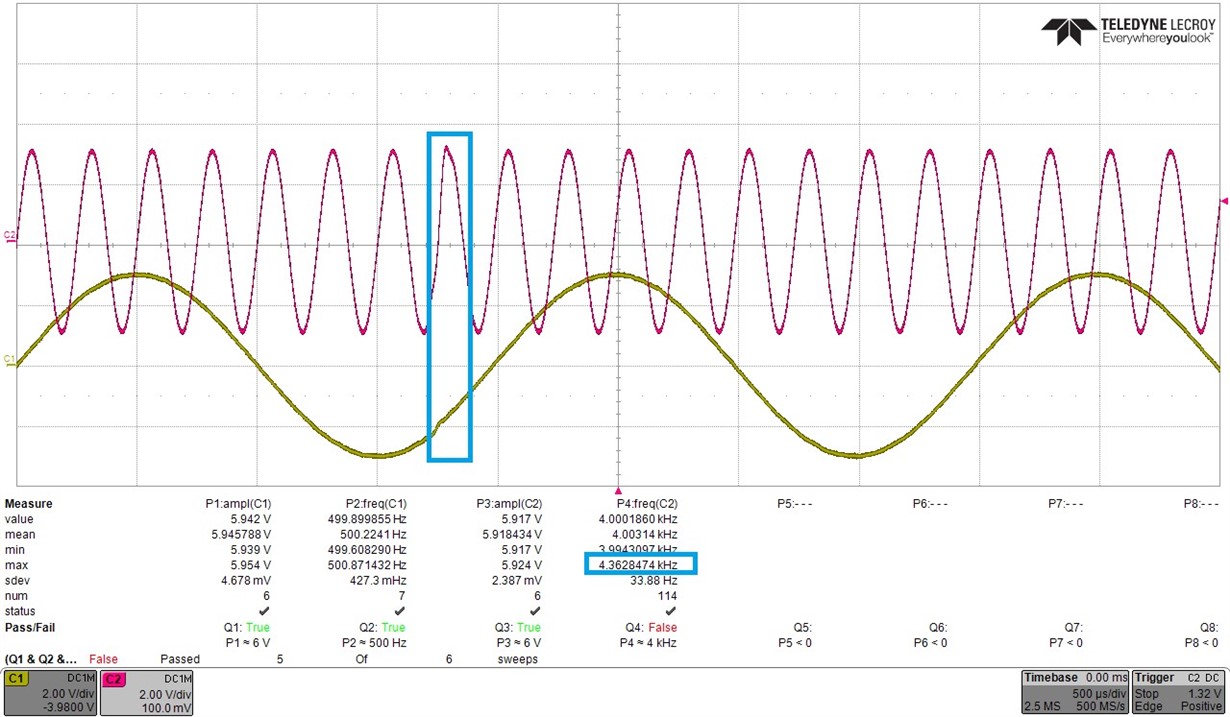

With such a configuration, some glitchs are present at the analog output of the DAC (refer to attached figure below). The glitch are very cyclic and appears on both channels at the same time.

When we change the configuration of the DAC to Clock Slave Mode with BCK PLL (3-Wire), the glitch are entirely gone.

Do you know what could possibly cause these glitches?