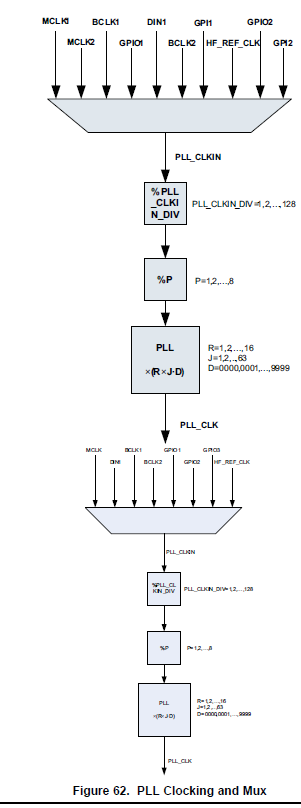

I am planning on using the on using the TLV320AIC3268 as an I2S Master with the PLL as my clock source. With the PLL_CLKIN being sourced from HF_REF_CLK.

- It appears that upon power up you must supply a clock signal (selected from Figure 63) to calibrate the HF_OSC_CLK. What is the recommended Frequency ranges for LFR_CLKIN?

- I saw a note saying that frequency could be off by approx ±7MHz. Is this a big impact on performance? Not sure if that’s a big deal or not. I could have another device provide the clock signal if it provides for better performance. Then I would use another input (Figure 62) for the PLL_CLKIN instead of HF_REF_CLK.