Hi All,

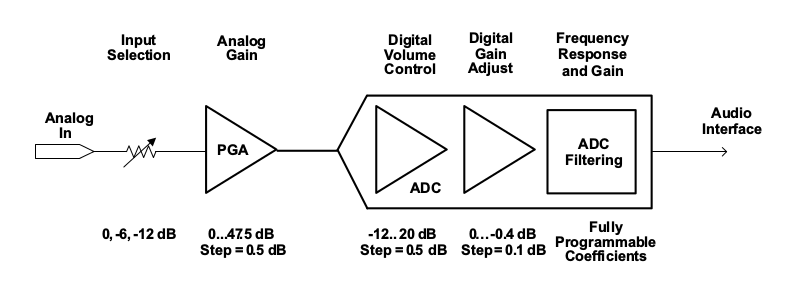

I am using AIC3268 in our design. Please help check:

(1) ADC Single-Ended input signal level is 0.5Vrms(CM=0.9). That means it could record full-scale audio data if input level up to 0.5Vrms in single-ended mode(Rin=10K and all gain control is set to zero). The recording data will be clipped if the input level over 0.5Vrms?

(2) ADC Differential input signal level is 1Vrms(CM=0.9). It is due to the max level of each analog input(IN1~IN4) is 0.5Vrms? After differential signal merge... it will be 2*0.5Vrms = 1Vrms before enter the ADC. Is it right?

(3) 0.5Vrms or 1Vrms is a limitation for ADC analog input ? If I choose large Rin such as 40K, it could increase the max capacity of input signal level?

BR,

Steven