Dear All,

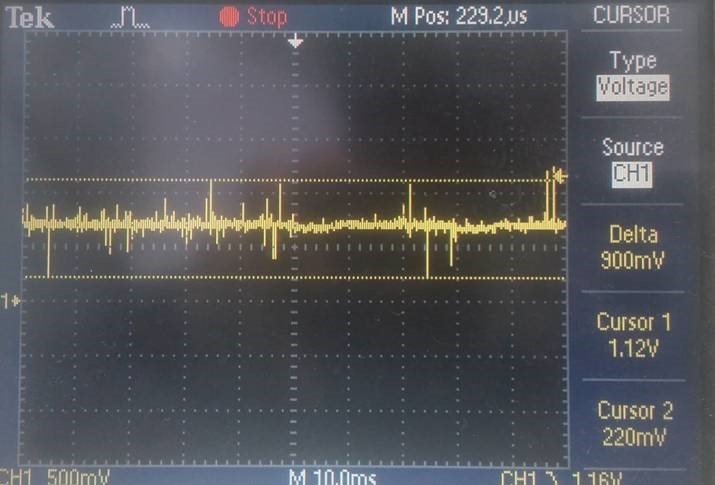

We got some trouble on PBTL wavform of TAS5751M.

Test conditions are PVcc=19V, RL=4ohm, Po=30W.

But there was an abnormal waveform like bellow waveform clip at about 16W output.

We think that there are some problem on PCB layout because this schematic is same as the schematic of EVM.

Also, there was no trouble on TAS5751M EVM.

Please review this PCB layout and abnormal waveform clip, then let me know the solution.

1. Schematic

2. Waveform

3. Layout

Regards

Jeffrey