Hi,

I'm trying to get the Fs 16kHz, SCLK = 32*Fs, MCLK = 256*Fs mode working, which is permitted for single-speed, software-controlled mode in the datasheet.

Ideally this wants a 4.096 MHz MCLK, however my MCLK source is just plain 4.0 MHz (and all other clocks derived down from that),

meaning about 2.3% under ideal, although there is no frequency tolerance mentioned in the datasheet.

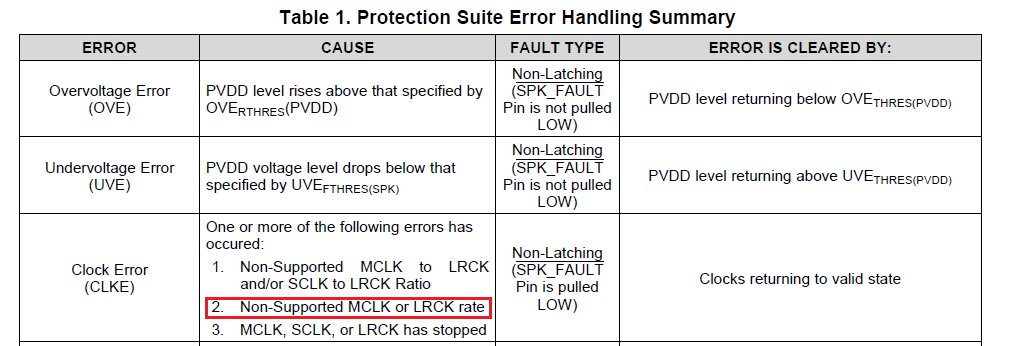

The part keeps giving me a steady CLKE error (bit 3 in register 8), which is supposed to be non-latching,

so it means the error is not recovering.

I've tried re-toggling /SPK_SD and reprogramming the registers after my clocks were already on, but this did not help.

(Possibly irrelevant info: although the part drives only one speaker, there is identical 16-bit I2S data in both I2S channels,

and I've tried but I've tried both BTL and PBTL settings but nothing changes).