Hi,

The TLV320ADC3101 supports a TDM + DSP multi-channel configuration of the i2s.

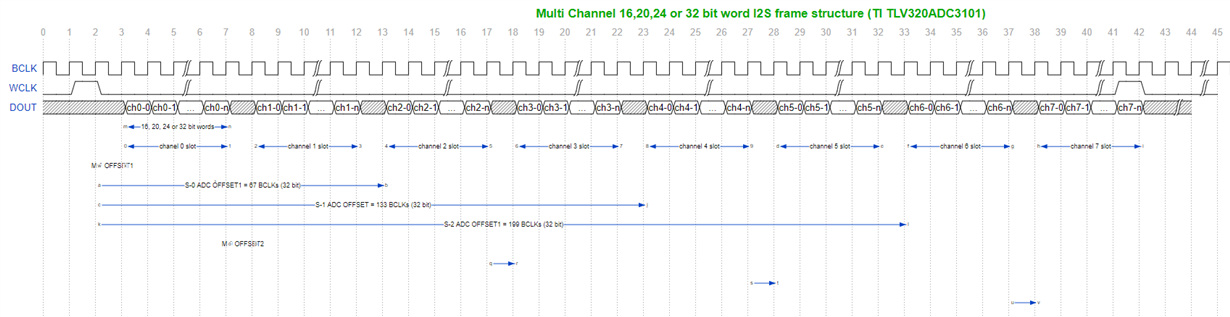

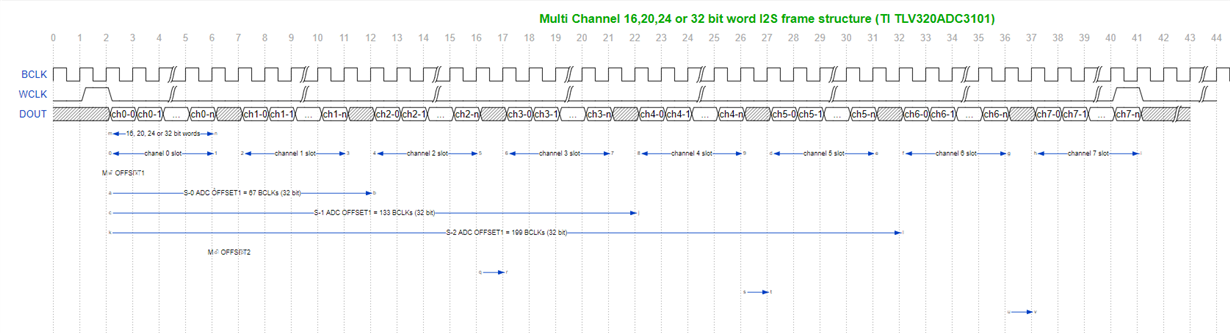

By connecting up 4 ADCs (1 master, 3 slave) and programming the various registers as follows (ADC udio interface control, i2s tdm control, data slot offset 1, data slot offset 2) over i2c, the expected i2s frame structure should be similar to the following:

Is there a model available of the ADC which will produce an expected i2s output depending on a given configuration, either in System verilog or C?

I have a configuration for the 4 ADCs which should produce the above output, but if possible would like to validate that config against a model of the TLV320ADC3101 part.

Any help here would be really appreciated.

Thanks,

Cian