I'm trying to test the DAC output by enabling the Beep..

I verified the 3.3v/1.8v are at the chip, and that it's not in reset.

The MClk (8Mhz) and BClk (1Mhz) also look good going to the DAC, where 1Mhz was chosen as approximately 16bits/ch * 2ch * 30kS/sec

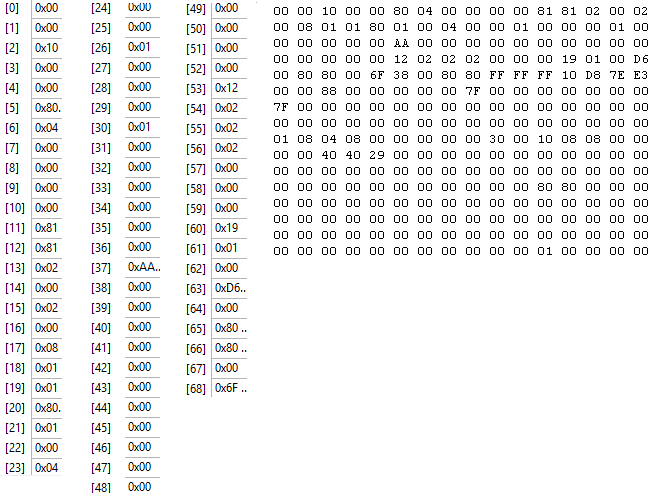

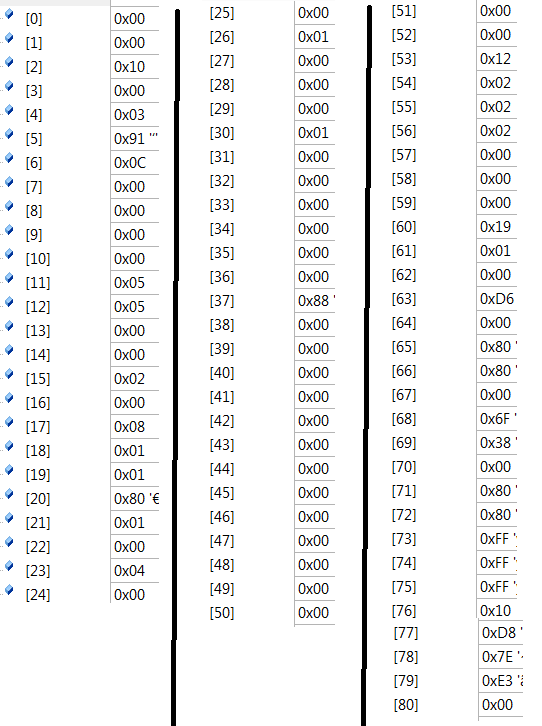

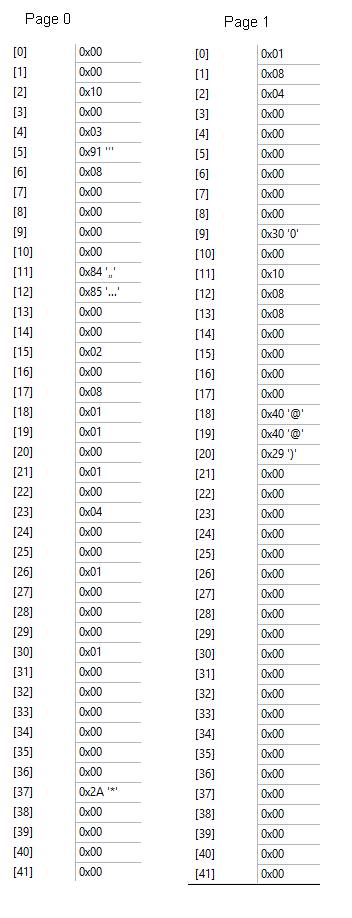

The register configuration follows the Example Setup 4.1, with the differences related to the Beep (ex. Processing Block P25 (Reg 0x3C = 0x19), Beep Length, Beep Enable*)

The readback of the registers match what I've written, however, there is no signal at the HPL/HPR pins.. the Beep Enable (Page 0 Register 0x47) always reads back 0x80 and is not resetting automatically, so it seems like it's not running, but I can't see what's wrong.

*Note, according to the Reference Guide, the Beep Enable is listed as being on Page 0, however in Section 2.4.5.1, it's described as being on Page 1.. I assume this is a typo in the document?