Other Parts Discussed in Thread: TLV320AIC33

Hello,

I have a communcation problem concerning I2S between a telit LE910-Module and the AIC3104 codec.

The i2c configuration interface, also a loopback configuration from LINE1LP to LEFT_LOP work fine.

My aim is to read a mono signal single ended from LINE1LP to I2S-Interface, and from I2S-Interface to LEFT_LOP single ended.

The I2S-configuration of the LE910-Master is:

Mode: TDMS

BCLK: 4096 kHz

Sample rate: 16 kHz

WCLK: 16 kHz highpulse for 1 BCLK-Clock with 256 Clocks per frame.

Bits per Sample: 16

The signal level ist 1.8V

I tried the following configuration

#!/bin/bash

# I2C-Busse suchen

modprobe i2c-dev

# Register 1: Software Reset Register

i2cset -y 7 0x18 0x01 0x80

sleep 1

# Register 102: Clock Generation Control Register: CLKDIV_IN uses BCLK, PLLCLK _IN uses BCLK

i2cset -y 7 0x18 0x66 0x62

####################################################################################################

# High speed mode: BCLK * 1 => J=24,D=0,R=1,P=1 (generate 12288 kHz internal clock from 4096kHz BCLK, fsref=48kHz, fs=16kHz)

# Page 0/Register 2: Codec Sample Rate Select Register (Sample-Rate fs=fsref/3)

i2cset -y 7 0x18 0x02 0x44

# Page 0/Register 3: PLL Programming Register A (PLL enable, P=1, Q=16)

i2cset -y 7 0x18 0x03 0x81

# Page 0/Register 4: PLL Programming Register B (J=24)

i2cset -y 7 0x18 0x04 0x60

# Page 0/Register 5: PLL Programming Register C (D=0)

i2cset -y 7 0x18 0x05 0x00

# Page 0/Register 6: PLL Programming Register D (D=0)

i2cset -y 7 0x18 0x06 0x00

# Page 0/Register 11: PLL Programming (R=1)

i2cset -y 7 0x18 0x0B 0x01

# Page 0/Register 9: Audio Serial Data Interface Control Register B DSP-Mode, 256 Bit, ADC-, DAC-Resync)

i2cset -y 7 0x18 0x09 0x4E

####################################################################################################

# Page 0/Register 19: MIC1LP/LINE1LP to Left-ADC Control Register

i2cset -y 7 0x18 0x13 0x04

# Page 0/Register 15: Left-ADC PGA Gain Control Register (Unmute Left PGA, set gain to 0 dB)

i2cset -y 7 0x18 0x0f 0x00

# Page 0/Register 7: Codec Data-Path Setup Register (Route Left data to Left DAC)

i2cset -y 7 0x18 0x07 0x08

# Page 0/Register 37: DAC Power and Output Driver Control Register (Power up Left DAC)

# ? HPLCOM configured as independent single-ended output? 0xa0

i2cset -y 7 0x18 0x25 0x80

# Page 0/Register 41: DAC Output Switching Control Register ( Left-DAC output selects DAC_L1 path to left line output driver.)

i2cset -y 7 0x18 0x29 0x00

# Page 0/Register 43: Left-DAC Digital Volume Control (Unmute Left digital volume control, set gain to 0 dB)

i2cset -y 7 0x18 0x2B 0x00

# Page 0/Register 82: DAC_L1 to LEFT_LOP/M Volume Control Register (Route Left DAC output to Left line outs)

i2cset -y 7 0x18 0x52 0x80

# Page 0/Register 86: LEFT_LOP/M Output Level Control Register (0dB Gain Left line outs, LEFT_LOP power up)

i2cset -y 7 0x18 0x56 0x09

The result is, that I neither get samples from the input nore I found samples from the DIN at the LEFT_LOP.

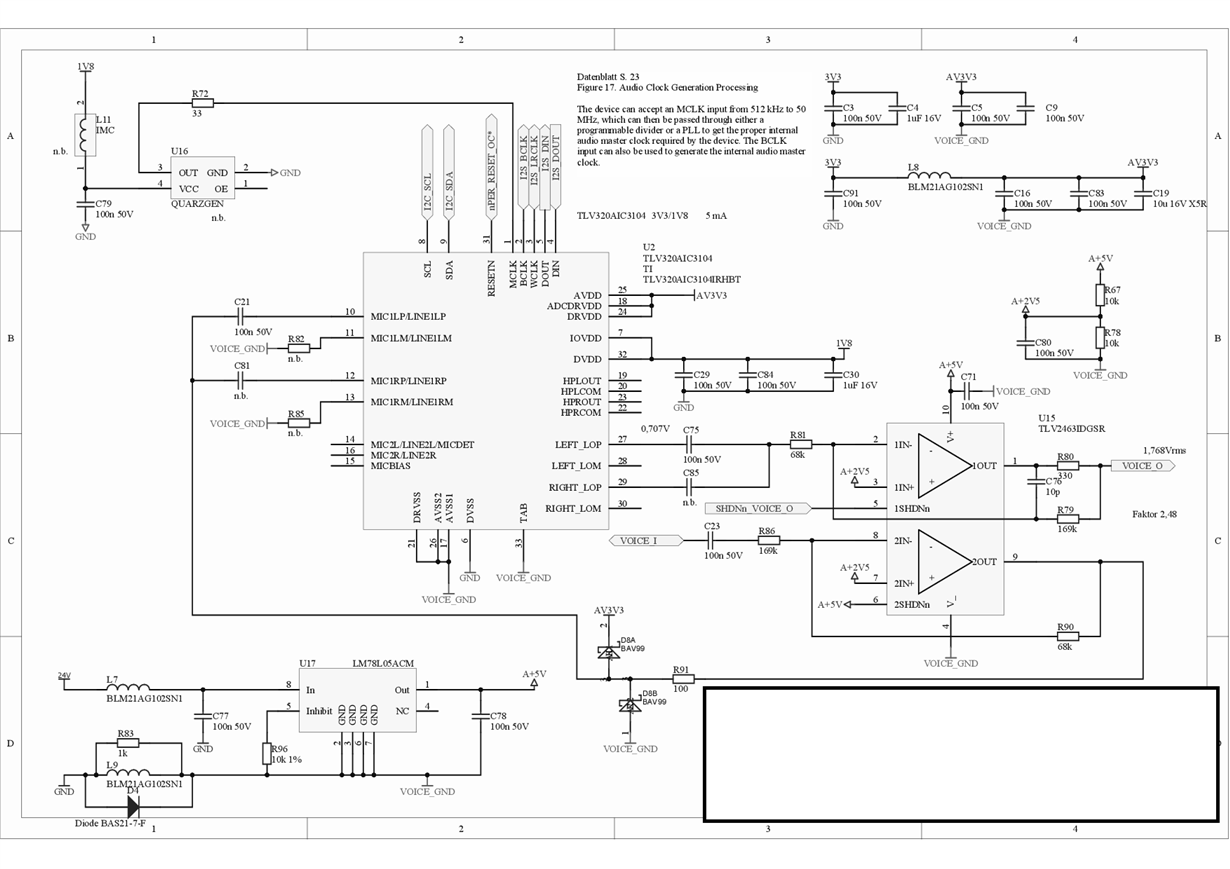

the schematic of the codec:

What is wrong with my configuration?

Kind regards

Gregor