Other Parts Discussed in Thread: DIX4192

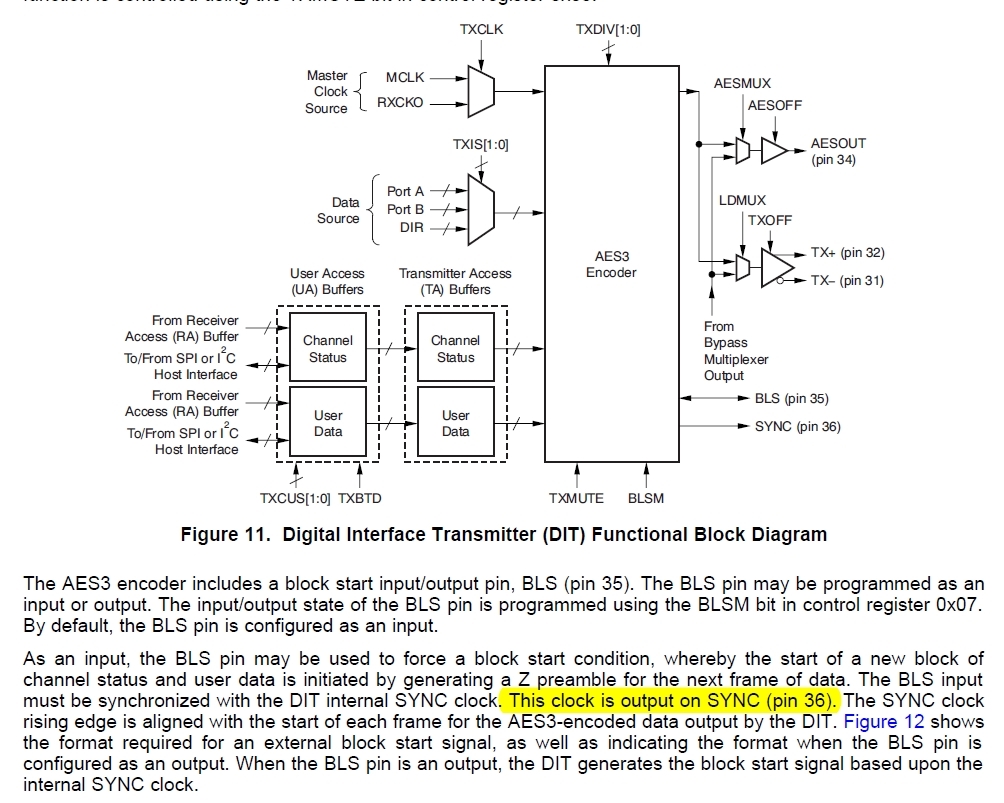

what is the founction of BLS and SYNC?

How should BLS and SYNC used in system?

Please give some examples of utility of BLS and SYNC.

DIX4192 is applied in our system to transfer I2S data to SPDIF (AES encode data).

what is the difference between the line driver output and the CMOS-buffered output to external logic of DIT ? Is the line driver used to drive long cables (far end)  and CMOS buffer used to drive circuits (near end)?

and CMOS buffer used to drive circuits (near end)?