Tool/software: Code Composer Studio

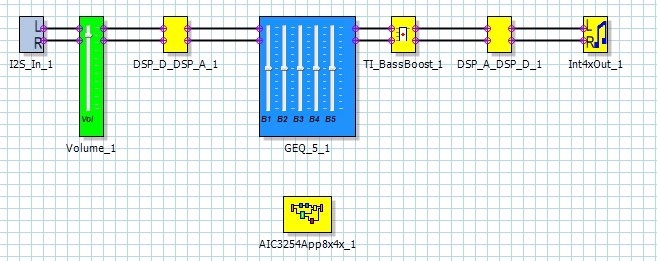

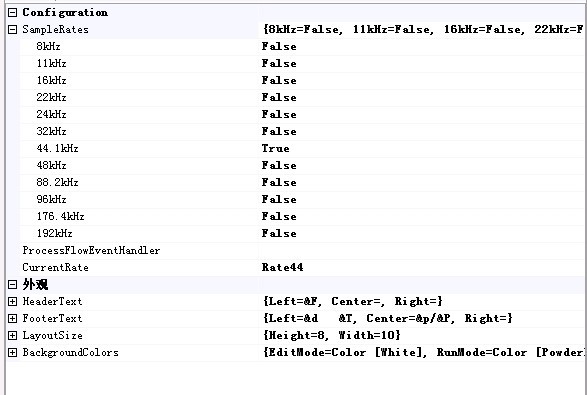

my ctm cinfig tlv320aic3254 like this pic

but the LOL/LOR has no signal out, and I2S has no output.

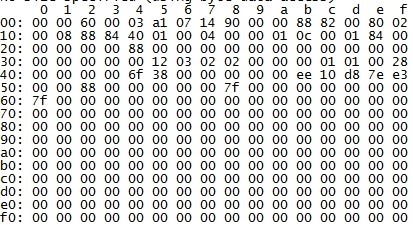

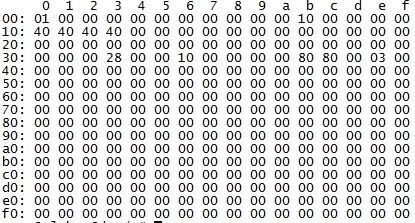

They guess there has something wrong with the config of PLL or power.

Any possible to share the config of the PLL and power and let ctm has some output first.

tlv320aic3254