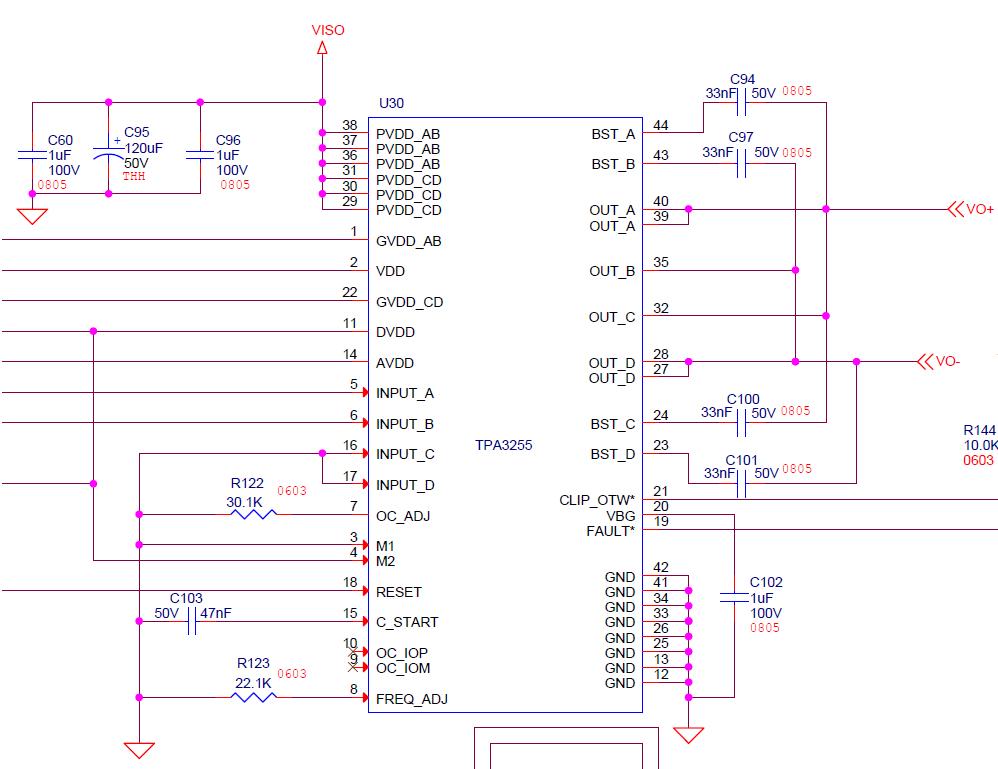

We are having an issue with our voltage on start up, if the PVDD is above 27 Volts we start and run correctly, but below that the output will not come on. If we start up at 27 volts and then turn the power down after start up the outputs will come on. This is not a 100% problem some boards work some don't. We are operating in PBTL mode, and see no fault indications on a scope. Any Ideas? We are not using this in a audio application so we are not concerned with distortion ect.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.