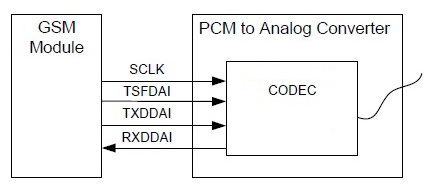

My customer want to clock the audio codec from external I2S bus. There are only 256 kHz BLCK has present.

They connect external BCLK signal to BCLK pin and configure it as required for 48 kHz audio. But this configuration don't work.

There are no limits for BLCK frequency provided in datasheet. At the same time MCLK limits at 512 kHz minimum.

The device can accept an MCLK input from 512 kHz to 50 MHz that can then be passed through either a programmable divider or a PLL to get the proper internal audio master clock required by the device. The BCLK input can also be used to generate the internal audio master clock.

Can you clarify limits of BCLK?

It's possible to clock the codec from 256 kHz?