hi

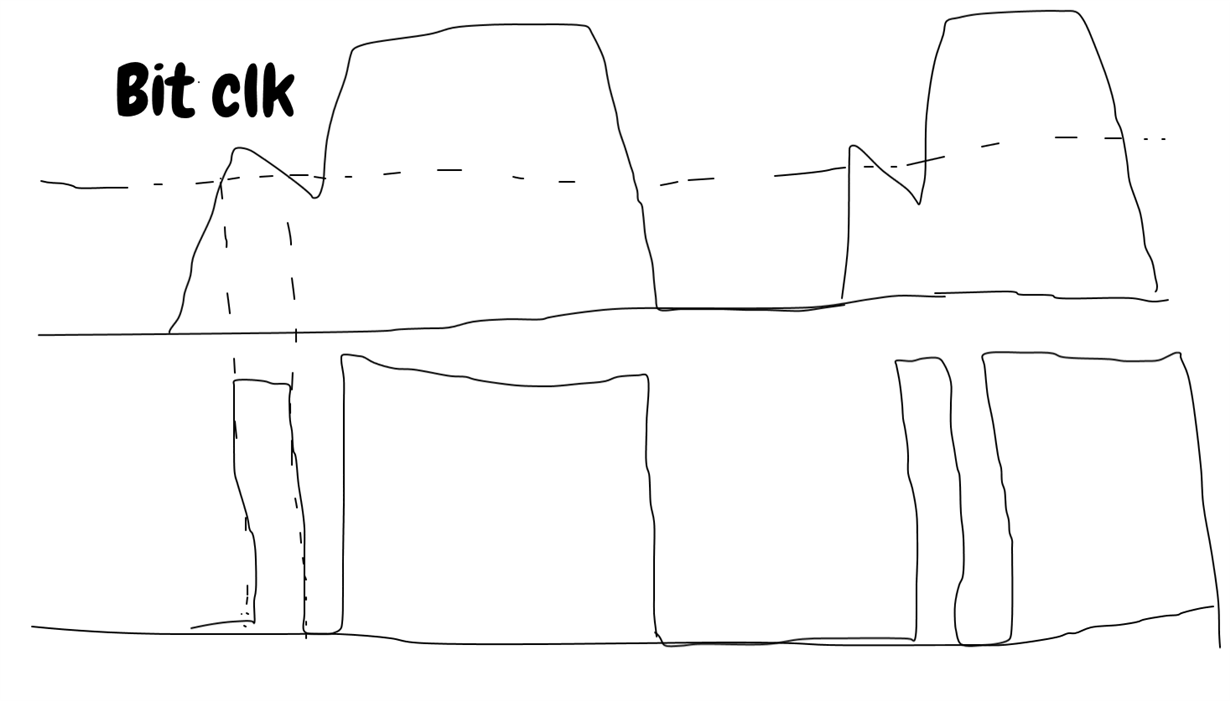

We have some strange behavior and we wish to ask about the digital inputs hysteresis, specifically for the I2S clicks and data.

what's the amplitude of a glitch that can cause a false value to be read?

any advices/guidelins on how to improve the noise immunity of PCM1792A?

thanks a lot in advance

KR

Vincenzo