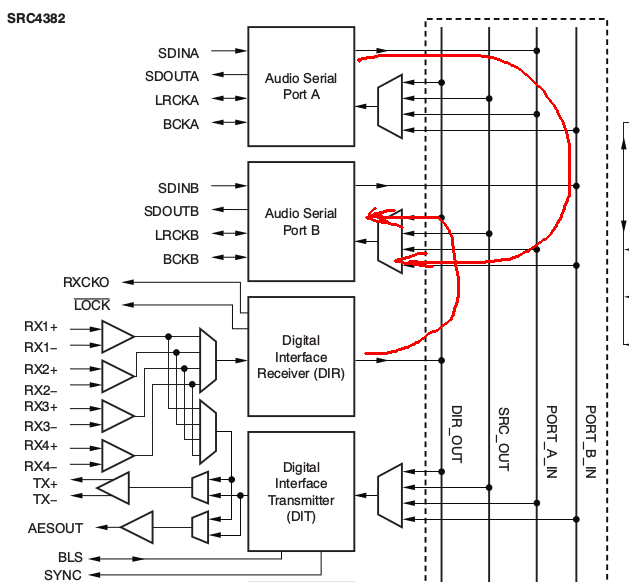

Part Number: SRC4382

Hi Team,

I would like to check with you, could we forward the signals coming from the DIR inputs and Port A I2S directly to Port B without passing through the ASRC, as below,

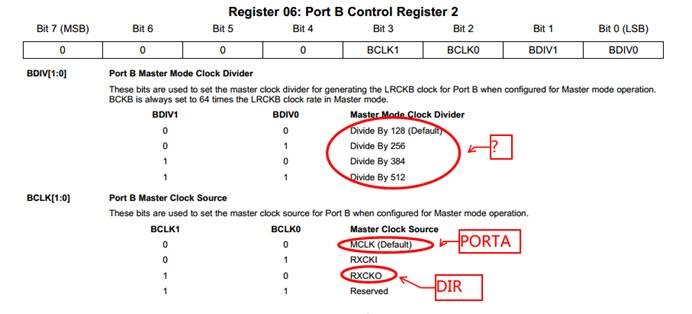

Another question is, if the sample frequency of PortA and DIR changes, how to tell PortB(Master mode) change its MCLK and LRCLK accordingly to keep input/output sample frequency the same? Seems SRC4382 can't get real time sample frequency of PortA and DIR.