Other Parts Discussed in Thread: AM5718, TAS2552,

Tool/software: Linux

Hello everyone.

We have developed our custom board with AM5718 processor in which we use the TAS2553 codec IC with 8ohm Speaker.

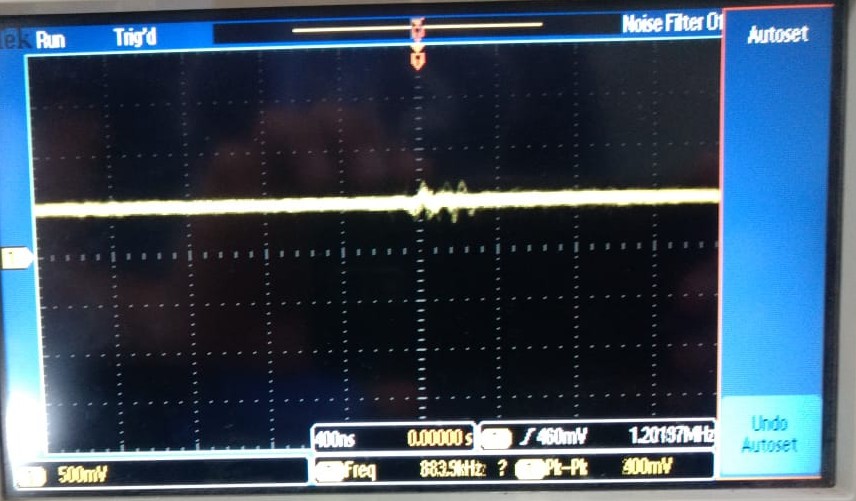

Please check the attached image for the connection of IC with AM5718.

We have done below chnages in dtsi as below.

sound0: sound0 {

compatible = "simple-audio-card";

simple-audio-card,name = "TAS2552";

simple-audio-card,widgets =

"Speaker", "Speaker";

simple-audio-card,routing =

"Speaker", "SPK";

simple-audio-card,format = "dsp_b";

simple-audio-card,bitclock-master = <&sound0_master>;

simple-audio-card,frame-master = <&sound0_master>;

simple-audio-card,bitclock-inversion;

simple-audio-card,cpu {

sound-dai = <&mcasp3>;

system-clock-frequency = <12000000>;

};

sound0_master: simple-audio-card,codec {

sound-dai = <&tas2552>;

system-clock-frequency = <1800000>;

};

};

&i2c3 {

status = "okay";

clock-frequency = <400000>;

tas2552: tas2552@40 {

#sound-dai-cells = <0>;

compatible = "ti,tas2552";

reg = <0x40>; /*because we have connected ADDR to gound o.w. it will be 0x41 if it is at VDD*/

vbat-supply = <&vmain>;

iovdd-supply = <&v3_3d>;

avdd-supply = <&ldo3_reg>;

enable-gpio = <&gpio7 24 GPIO_ACTIVE_HIGH>;

status = "okay";

};

}

We have modified the pinmux in uboot-spl as below.

{XREF_CLK2, (M0 | PIN_INPUT)}, /* xref_clk0

{MCASP3_ACLKX, (M0 | PIN_INPUT_PULLDOWN)}, /* mcasp3_aclkx.mcasp3_aclkx */

{MCASP3_FSX, (M0 | PIN_INPUT_SLEW)}, /* mcasp3_fsx.mcasp3_fsx */

{MCASP3_AXR0, (M0 | PIN_INPUT_SLEW)}, /* mcasp3_axr0.mcasp3_axr0 */

{MCASP3_AXR1, (M0 | PIN_INPUT_SLEW)}, /* mcasp3_axr1.mcasp3_axr1 */

We have added the "clk_id=TAS2552_PLL_CLKIN_1_8_FIXED;" line in "tas2552_set_dai_sysclk" api of tas2552 codec driver to enable the 1.8 Mhz internal oscillator.

Now we are testing the different wav files using below command but sound does not proper.

root@am57xx-evm:~# amixer controls

numid=2,iface=MIXER,name='DIN source'

numid=3,iface=MIXER,name='Input selection'

numid=1,iface=MIXER,name='Speaker Driver Playback Volume'

root@am57xx-evm:~# amixer cget numid=1

numid=1,iface=MIXER,name='Speaker Driver Playback Volume'

; type=INTEGER,access=rw---R--,values=1,min=0,max=31,step=0

: values=0

| dBscale-min=-7.00dB,step=1.00dB,mute=0

root@am57xx-evm:~# amixer cset numid=1 50%

numid=1,iface=MIXER,name='Speaker Driver Playback Volume'

; type=INTEGER,access=rw---R--,values=1,min=0,max=31,step=0

: values=16

| dBscale-min=-7.00dB,step=1.00dB,mute=0

root@am57xx-evm:~# aplay /usr/bin/bass.wav

Playing WAVE '/usr/bin/bass.wav' : Signed 16 bit Little Endian, Rate 44100 Hz, Stereo

root@am57xx-evm:~# aplay /usr/bin/ooh.wav

Playing WAVE '/usr/bin/ooh.wav' : Signed 16 bit Little Endian, Rate 44100 Hz, Stereo

Please help us to solve our issue.

Thanks & Best Regards;

Nikunj Patel