Hi,

We've selected your TLV320AIC3204 Codec for use with a modem from Sierra Wireless and i'm having a bit of trouble configuring it to talk to the modem correctly.

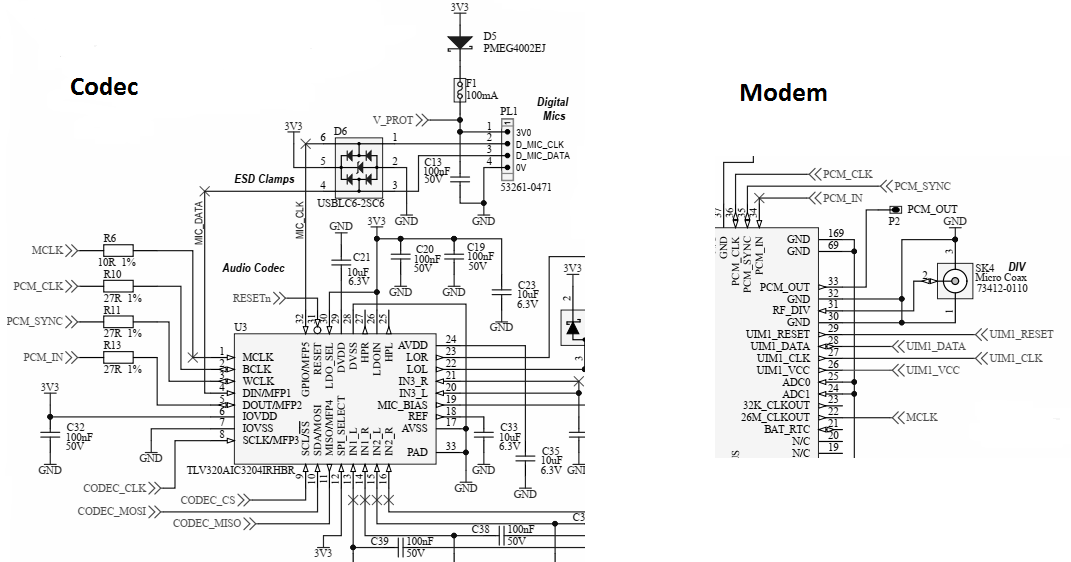

Our system is as follows:

Host microcontroller to setup the codec via SPI at 3.3V, MCLK is fed from the Modem which has a 26MHz CLKOUT pin. BCLK is connected to the modem PCM_CLK, WCLK to PCM_SYNC and DOUT to PCM_IN on the modem.

We think we've already made one mistake with the design as the Modem operates at 1.8V for it's general GPIO but makes no mention of voltage levels for PCM and our IOVDD on the codec is pulled up to 3.3V to interface with the microcontroller. It would be appreciated if you could confirm that the PCM levels should be at IOVDD level before we make any changes or adjustments

Secondly I've had mixed results configuring the codec, under some circumstances i'm able to ring the modem and hear nothing but silence, but under others i'm able to hear a lot of white noise.

Below is our startup configuration which results in white noise when calling the modem. If you have any suggestions that would be most appreciated.

Processor_Codec_WriteRegister(0x00, 0x00); // Page0 Processor_Codec_WriteRegister(0x01, 0x01); Processor_Codec_WriteRegister(0x12, 0x81); // Set NADC to 1 Processor_Codec_WriteRegister(0x13, 0x82); // Set MADC to 2 Processor_Codec_WriteRegister(0x14, 0x80); // Set AOSR to 128 Processor_Codec_WriteRegister(0x3D, 0x01); // Select ADC PRB_R1 Processor_Codec_WriteRegister(0x00, 0x01); // Page 1 Processor_Codec_WriteRegister(0x01, 0x08); // Turn off weak LDO Processor_Codec_WriteRegister(0x02, 0x01); // Turn on LDO Processor_Codec_WriteRegister(0x0A, 0x7B); // Set Vcm to 0.75V Processor_Codec_WriteRegister(0x3D, 0x00); // Select ADC PTM_R4 Processor_Codec_WriteRegister(0x47, 0x32); // Set Mic PGA to 3.1ms Processor_Codec_WriteRegister(0x7B, 0x01); // Set ref charge time to 40ms Processor_Codec_WriteRegister(0x0E, 0x02); // LOL Routing Processor_Codec_WriteRegister(0x0F, 0x02); // LOR ROuting Processor_Codec_WriteRegister(0x12, 0x00); // LOL Unmute Processor_Codec_WriteRegister(0x13, 0x00); // LOR Unmute Processor_Codec_WriteRegister(0x34, 0x20); // IN1_L to PGA_L Processor_Codec_WriteRegister(0x36, 0x02); // CM_ to M_L Processor_Codec_WriteRegister(0x37, 0x20); // IN1_R to PGA_R Processor_Codec_WriteRegister(0x39, 0x02); // CM to M_L Processor_Codec_WriteRegister(0x3B, 0x0C); // Unmute PGA_L Processor_Codec_WriteRegister(0x3C, 0x0C); // Unmute PGA_R Processor_Codec_WriteRegister(0x33, 0x68); // Set mic bias to 2V Processor_Codec_WriteRegister(0x00, 0x00); Processor_Codec_WriteRegister(0x51, 0xC0); // Power up ADC L&R Processor_Codec_WriteRegister(0x1D, 0x10); // Unmute L&R Processor_Codec_WriteRegister(0x52, 0x00);

For reference: The modem is setup to be a PCM Master, sampling clock edge control is on the rising edge and the PCM bit clock is 512 KHz.

My colleague has been able to configure the modem to pass audio from the IN1_R and IN1_L to LOR and LOL by bypassing the ADC/DAC blocks, so we think the codec is functioning correctly, just not sure about the codec configuration.

Thanks for your time.