Other Parts Discussed in Thread: PUREPATH-CMBEVM,

Hello,

I am trying to determine from the TAS5825M datasheet, what fault events will cause the output of the amplifier to turn off or shut-down. I believe the following conditions may cause the amp output to shut-off or shut-down:

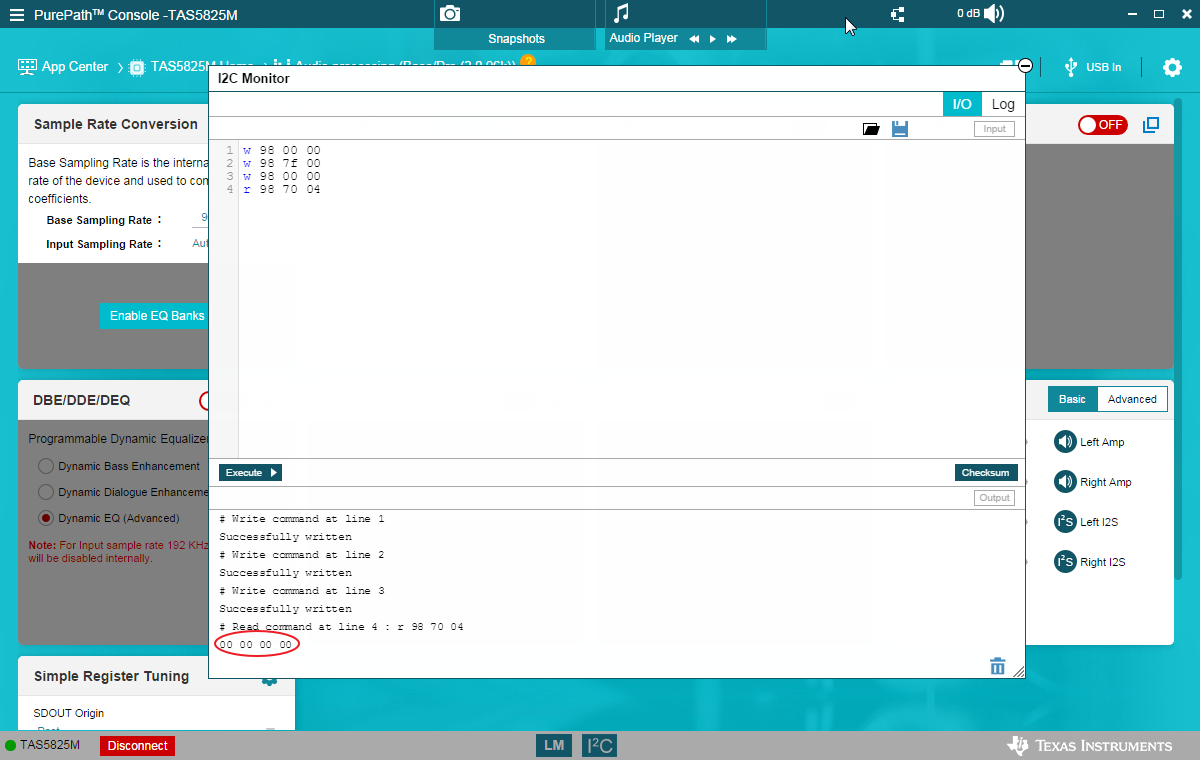

CHAN_FAULT Register (Offset = 70h) [reset = 0x00]

CH1_DC_1 left channel DC fault, CH2_DC_1 right channel DC fault

GLOBAL_FAULT1 Register (Offset = 71h) [reset = 0h]

DVDD_UV_I DVDD UV fault, DVDD_OV_I DVDD OV fault

PVDD_OV_I PVDD OV fault, PVDD_UV_I PVDD UV fault

GLOBAL_FAULT2 Register (Offset = 72h) [reset = 0h]

CBC_FAULT_CH2_I right channel cycle by cycle over current fault, CBC_FAULT_CH1_I left channel cycle by cycle over current fault

OTSD_I over temperature shut down fault

I am looking specifically for what events can cause the output audio to interrupt momentarily or to shut-off or shut-down.

Thank you and kind regards,

John

PVDD OV fault, PVDD UV fault

DVDD OV fault, DVDD UV fault

OTSD_I Over Temperature Shutdown fault