Other Parts Discussed in Thread: OPA1654

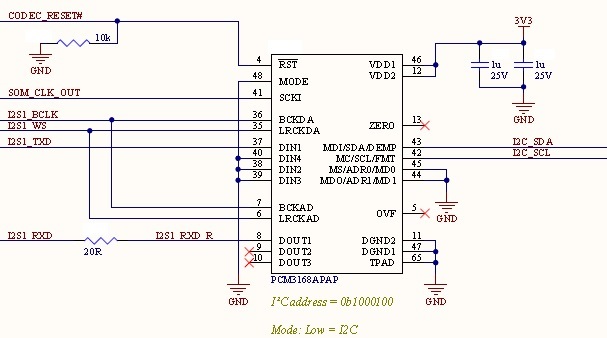

We are using a PCM3168A CODEC in our design and we are having some issues.

When powering-on (or power cycled), there is a chance that the CODEC will hold SDA low while in reset. We are using a pull-down to hold the CODEC in reset until the processor can boot and is ready to interface with the device. Once out of reset, the CODEC seems to sample the MODE pin correctly and, I will be testing a patch tomorrow to confirm, it works correctly despite the odd behavior during power-on. This normally wouldn't be an issue - however, the pin that is being used for I2C is required during the boot sequence of our iMX6 processor. If held low during power on, it prevents our processor from booting. This creates a deadlock that we cannot get out of.

We will be looking into pin swap the I2C signals during the next spin as this will avoid the deadlock. However, we are trying to understand what in the boot sequence can cause the I2C_SDA signal to remain low. We have numerous units already produced and we need to understand this to understand how it will affect the units we have in field.

From the datasheet:

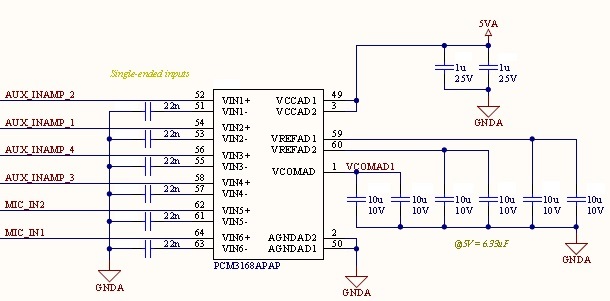

Section 9.3.6 : The PCM3168A device does not require particular power-on sequences for VCC and VDD; it allows VDD on and then VCC on, or VCC on and then VDD on.

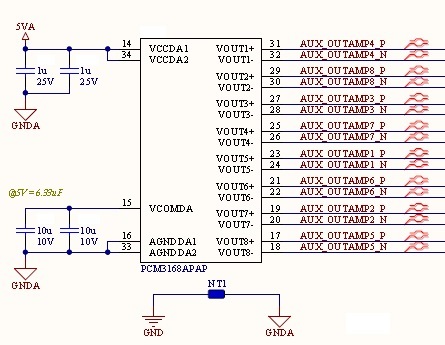

Section 12.1.1: Although the PCM3168A device has two power lines to maximize the potential of dynamic performance, using one common source (for instance, a 5-V power supply for VCC and a 3.3-V power supply for VDD generated from one common source) is recommended to avoid unexpected power-supply trouble such as latch-up or incorrect power-supply conditions. Also, simultaneous power-on/off of VCC and VDD is recommended to avoid unexpected transient responses in outputs, though the power-supply sequence of VCC and VDD is not specified in the operation and absolute maximum ratings point of view.

Our current power supply scheme powers both rail nearly-simultaneously. I also modified our power sequencing to delay the 3V3 rail until the 5V rail had powered-up, as would be the case if the 3V3 rail were to be generated with the 5V rail, to no avail.

Background information on the application:

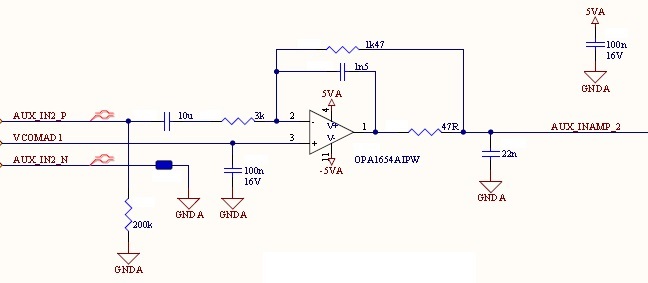

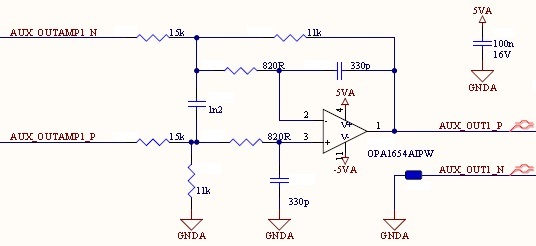

- All 6 AD inputs are used in single-ended with OPA1654, 22nF capacitors to AGND on VINn- signals.

- All 8 DA outputs are used with OPA1654.

UPDATE 2018-12-05:

A patch using a bi-directional signal buffer with output enable (OE) connected to the CODECs reset (RST#) works. Once the iMX6 boots and asserts the RST# line high, the CODEC is fully operational. So this odd behavior is only present during the reset of the CODEC.