Other Parts Discussed in Thread: PCM1808

Hi.

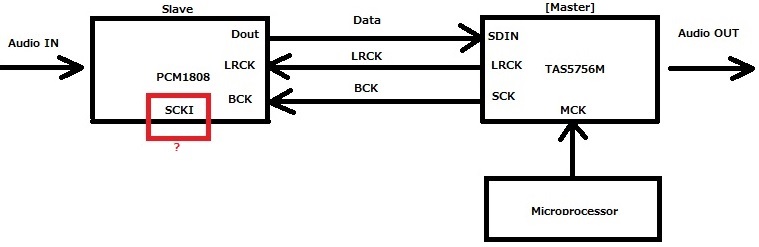

I'm planning sound system below.

I cannot provide audio rate clock to TAS5756M.

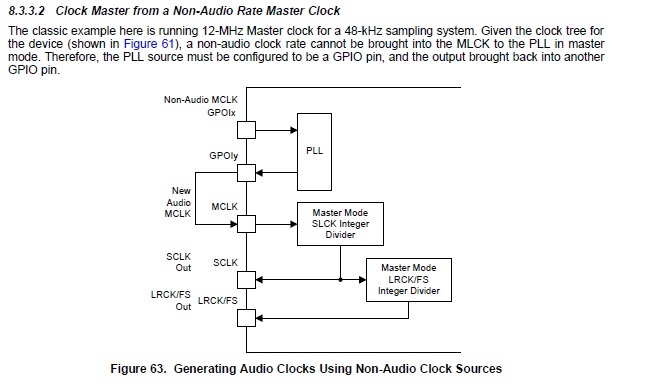

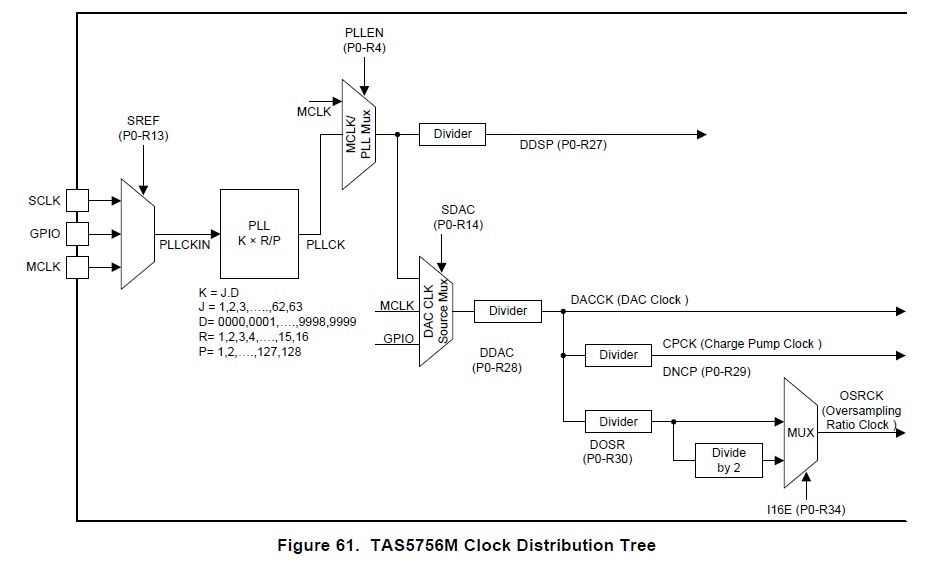

So I'll use TAS5756M "non-Audio rate master clock" mode like below diagram of datasheet.

("non-Audio rate clock" will be provided from microprocessor in my system....)

(TAS5756M Datasheet page 36)

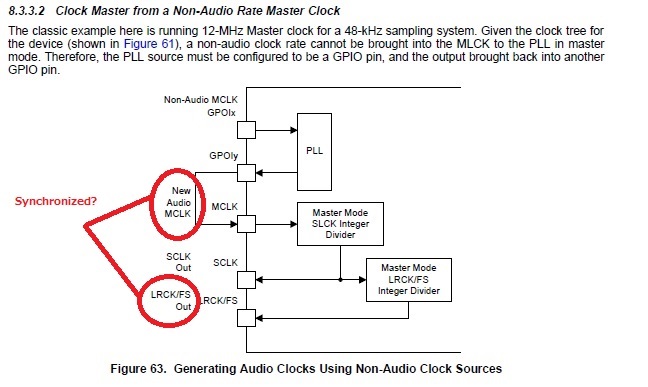

I'm planning that using "New Audio MCLK" in above Figure.63 as SCKI of PCM1808 too.

According to PCM1808 datasheet, this device requires synchronization of LRCK between SCKI.

Like a below...

"7.3.3 Synchronization With Digital Audio System

In slave mode, the PCM1808 device operates under LRCK (pin 7), synchronized with system clock SCKI (pin 6).

The PCM1808 device does not require a specific phase relationship between LRCK and SCKI, but does require

the synchronization of LRCK and SCKI."

(PCM1808 datasheet Page 15)

I worry about this.

The LRCK & MCK(new audio mck) from TAS5756M are synchronized?

(Do I need set some register to synchronize these?)

Thank you.