Dear Sir.

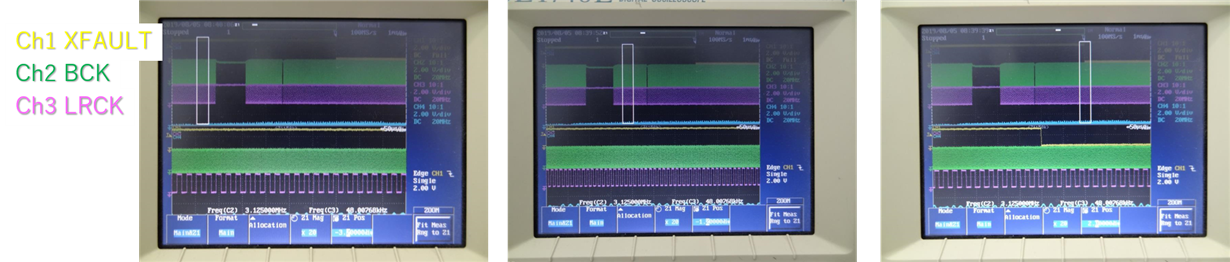

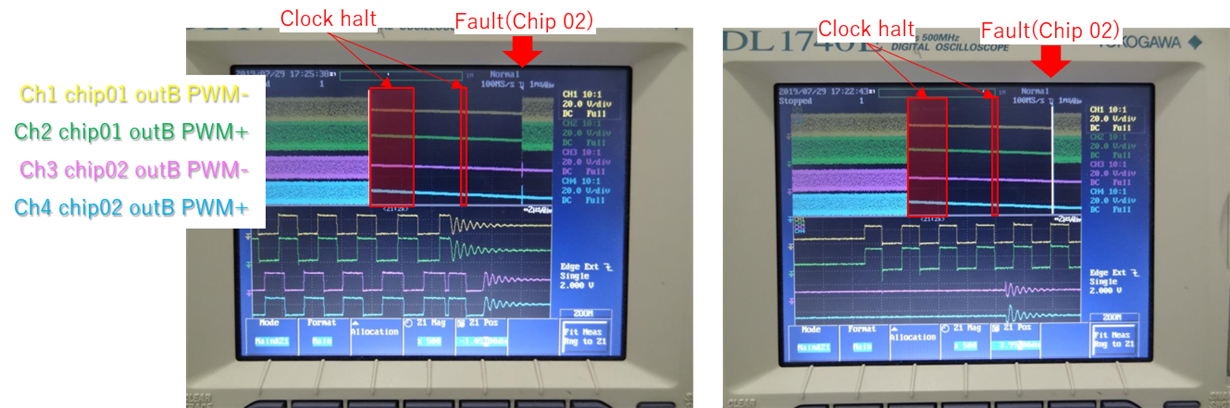

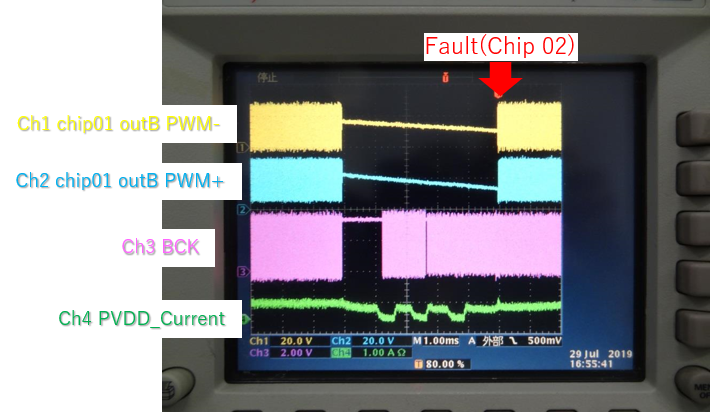

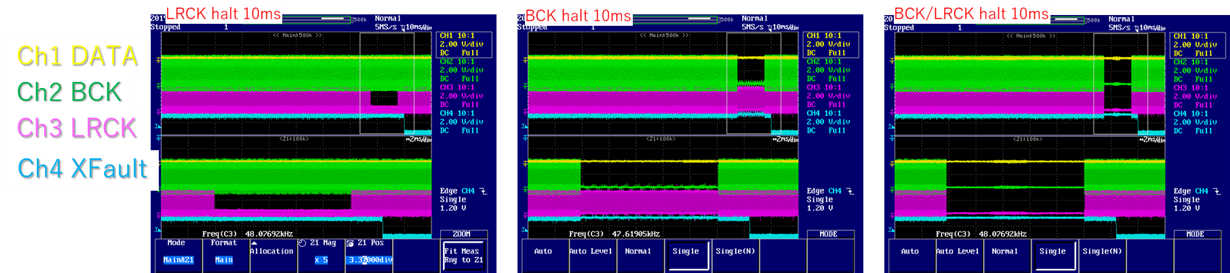

Our system breaks off SCK and LRCK when changeing function or chpater.

During that, TAS5825 sometimes occurs OCP

(register value: x70=01, x71=04, x72=00)

Couldd you reply below questins?

1. In the first place, Does TAS5825 support the system whose SCK and LRCK often break off?

2, When SCK and LRCK halt or auto recovery, does this device need to comply some kind of procedures?

ex.) Timing among SCK,LRCK,DATA,

During clock break off, they should fix Low level or High level, or no requirement

3. MASK CLK_FAULT(Bit 4) of PIN_CONTROL1 register (0x74) is set 1(MASK), in our system.

Does this bit only control Fault pin, or change the process for clock error (all channels into Hi-Z)?

4. Do you have any other advise for this issue?