Other Parts Discussed in Thread: TLV320AIC3104

Hi expert:

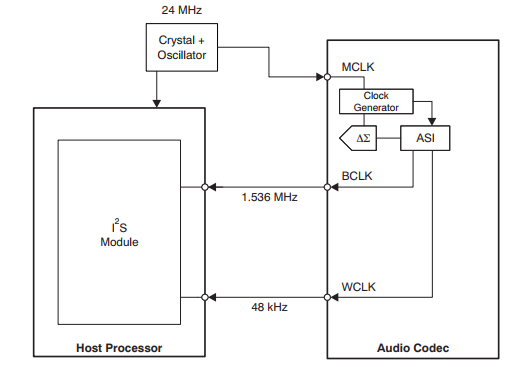

About the codec TLV320AIC3104 ,in our case,it is in the master mode,now we want to know that:

How to generate the MCLK to TLV320AIC3104,and what type clock it can received,an external OSC?but it output the sinewave,psl help to confirm.

Thanks!