Hi,

Is my understanding correct that PCM1753 perform the dc offset calibration for the outputs of VOUTL and VOUTR during the reset period(1024 system clocks)?

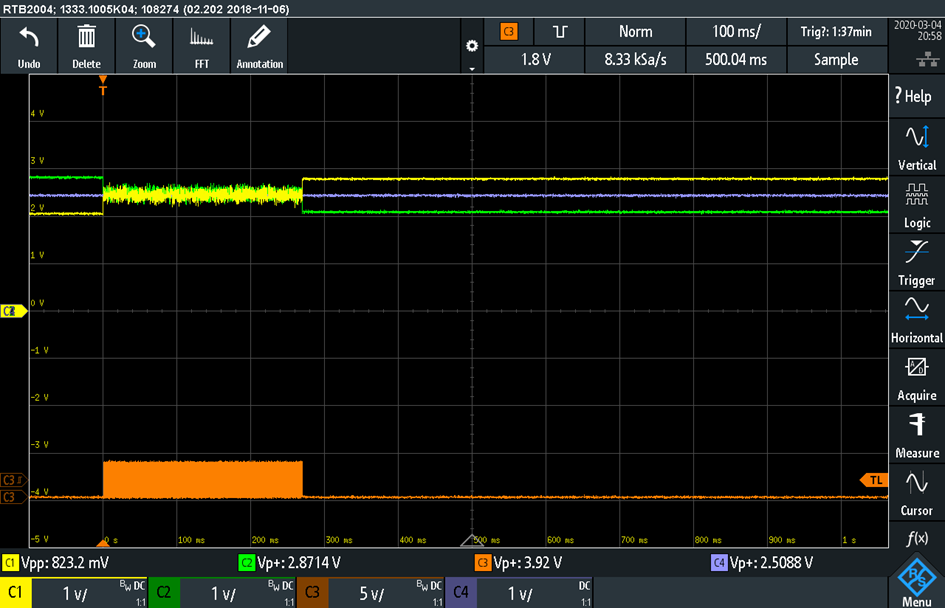

It seems that the dc offset is cancelled when observing VOUTL and VOUTR.

Best regards,

Kato