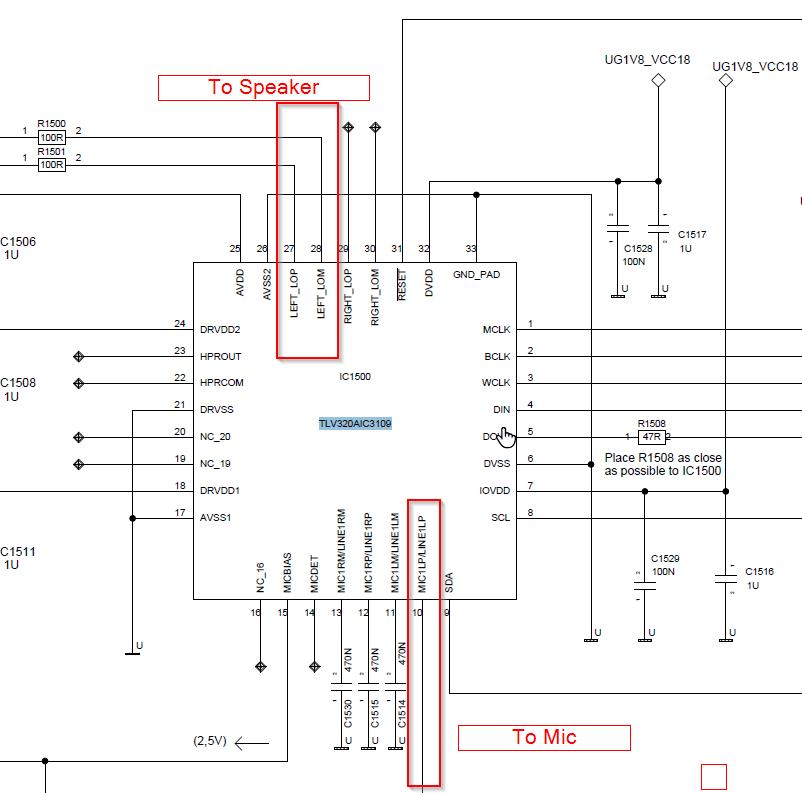

We are using the TLV320AIC3109-Q1 Codec with above mic and speaker connection. The Codec is Connected to SOC over I2S. I2S is configured in left Justified.

Sample Rate : 16000 Hz

Bit Depth : 16 bits

BitRate : 512Khz

Below are the register settings we are using .

| Codec Register | Description | Comments | C2 Verified Values |

| 1( 0x01) | Software Reset Register | 0x00 | |

| 2 (0x02) | Codec Sample Rate Select Register | 0x44 | |

| 3 (0x03) | PLL Programming Register A | 0x81 | |

| 4 (0x04) | PLL Programming Register B | 0xc0 | |

| 5 (0x05) | PLL Programming Register C( | 0x00 | |

| 6 (0x06) | PLL Programming Register D( | 0x00 | |

| 7 (0x07) | Codec Data-Path Setup Register | 0x08 | |

| 9 (0x09) | Audio Serial Data Interface Control Register B | 0xC0 | |

| 10 (0x0A) | Audio Serial Data Interface Control Register C | 0x01 | |

| 11 (0x0B) | Audio Codec Overflow Flag Register | 0x04 | |

| 12 (0x0C) | Audio Codec Digital Filter Control Register | 0x54 | |

| 15 (0x0E) | ADC PGA Gain Control Register | 0x00 | |

| 16 (0x0F) | Auxiliary PGA Gain Control Register | 0x80 ( 0x00) | |

| 19 (0x13) | MIC1P/LINE1P to ADC Control Register | 0x06 | |

| 21(0x15) | MIC2P/LINE2P to ADC Control Register | 0x78 | |

| 22 (0x16) | reserved. DNP | 0x78 (0x07) | |

| 24 (0x18) | reserved. DNP | 0x78 (0x00) | |

| 25 (0x19) | MICBIAS Control Register | 0x86 | |

| 37 (0x25) | DAC Power and Output Driver Control Register | 0x80 | |

| 41 (0x29) | DAC Output Switching Control Register | 0x00 | |

| 42 (0x2A) | Output Driver Pop Reduction Register | 0x16 | |

| 43 (0x2B) | DAC Digital Volume Control Register | To be Adjusted based on measurement | 0x00 |

| 82 (0x52) | DAC_1 to LEFT_LOP/M Volume Control Register | 0x80 | |

| 86 (0x56) | LEFT_LOP/M Output Level Control Register | 0x0b is the value read. To be Investigated | 0x09 |

| 101 (0x65) | Clock Register | 0x00 | |

| 102 (0x66) | Clock Generation Control Register | 0xa2 | |

| 107 (0x6B) | New Programmable ADC Digital Path and I2C Bus Condition Register | 0x00 | |

| 109 (0x6D) | DAC Quiescent Current Adjustment Register | 0xc0 |

We are observing few issues with the above settings.

1) The microphone does not work when the registers 22 and 24 are programmed with reserved values. The Mic works only when programmed with values for register 22 -> 0x07 , 24 -> 0x00 , 16 -> 0x00

2) When the above values are programmed we observe there microphone is having noise. (Attached the audio file for reference)