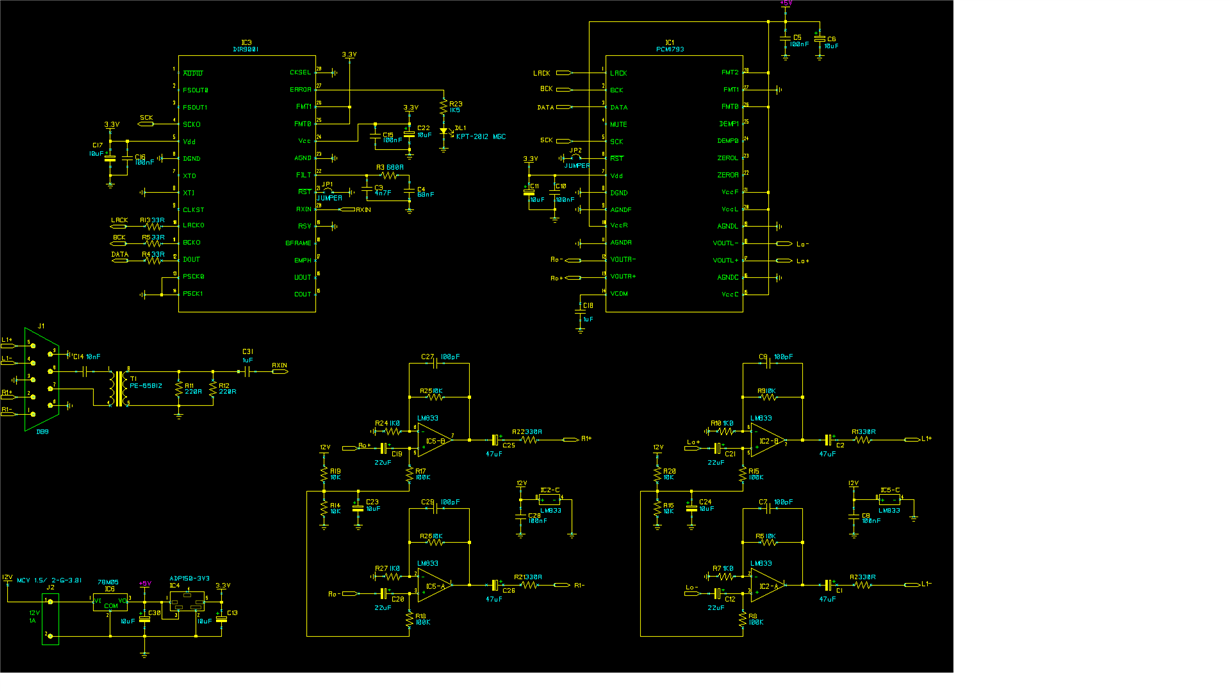

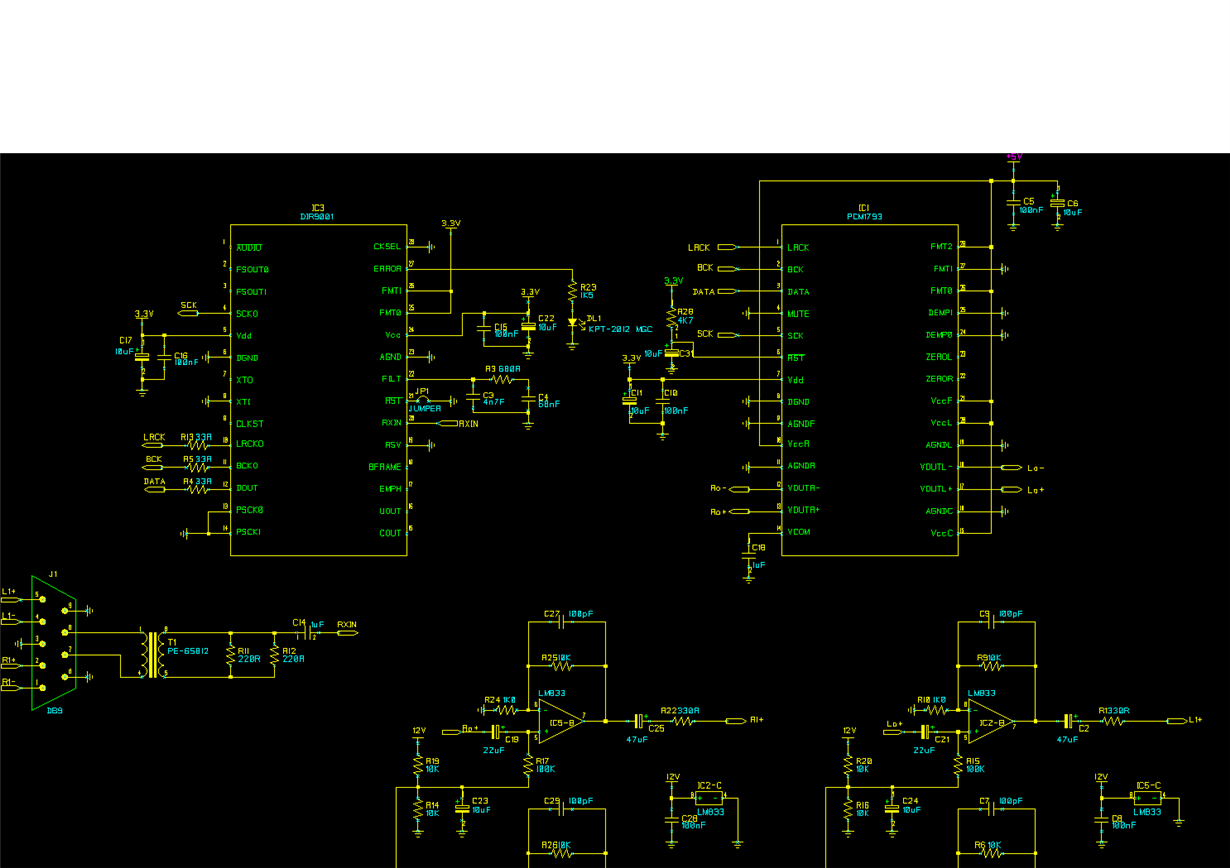

Other Parts Discussed in Thread: DIR9001, , LM833

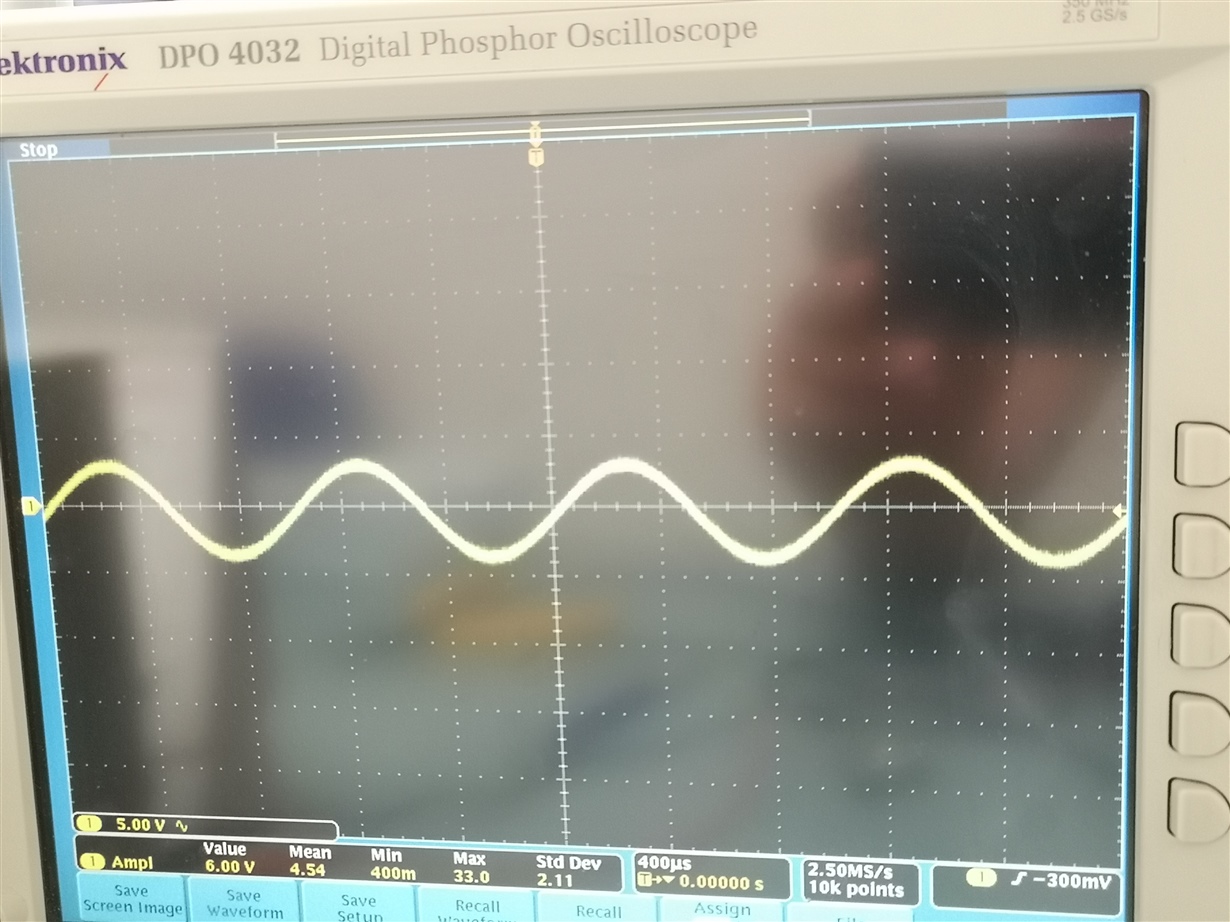

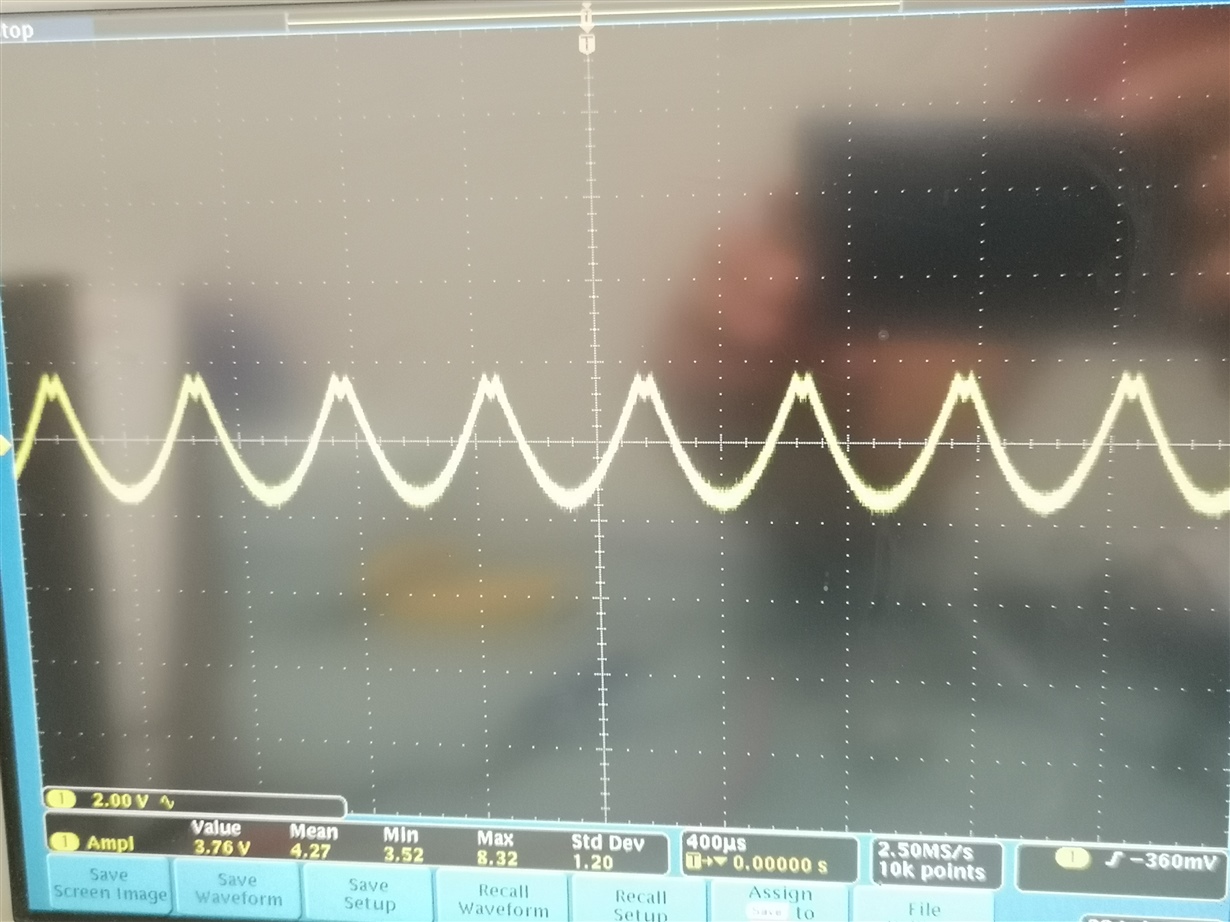

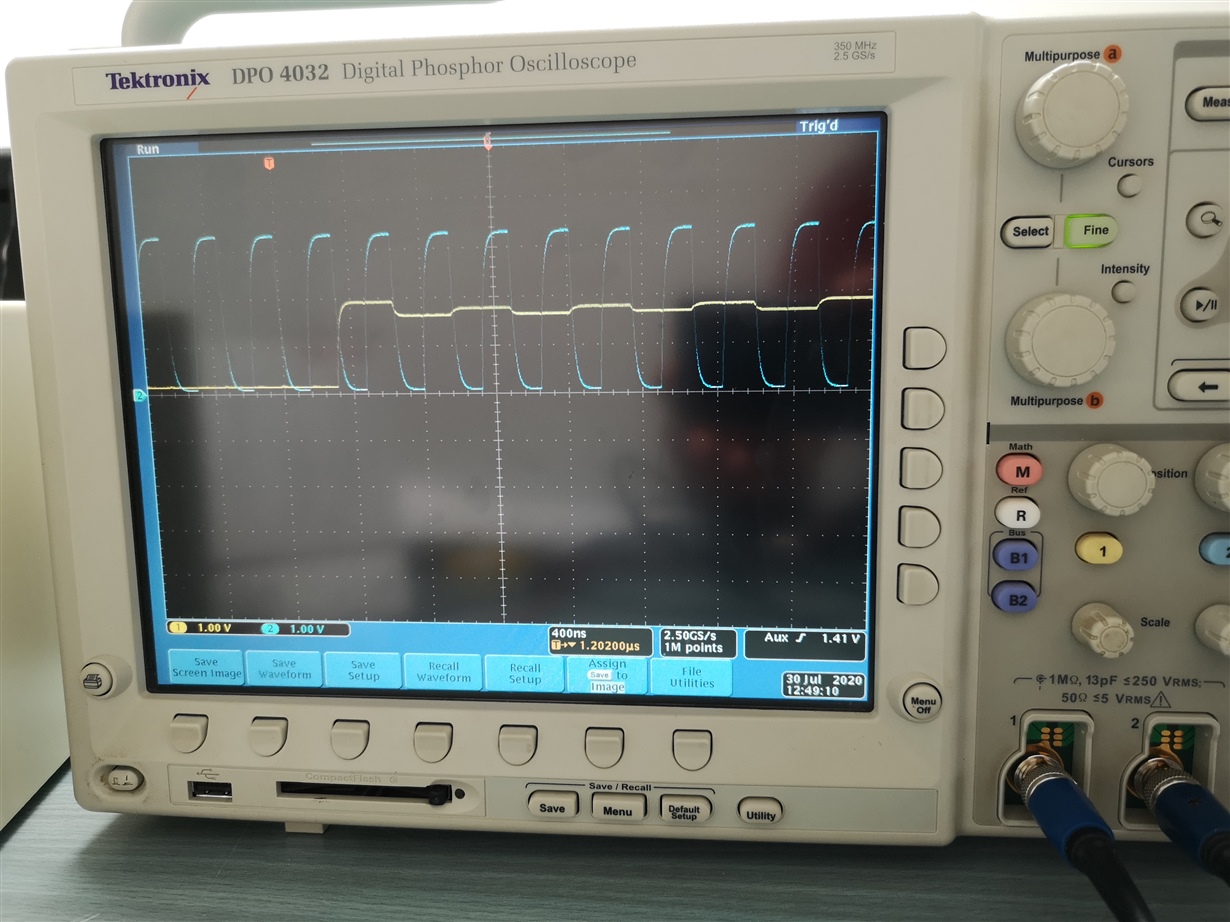

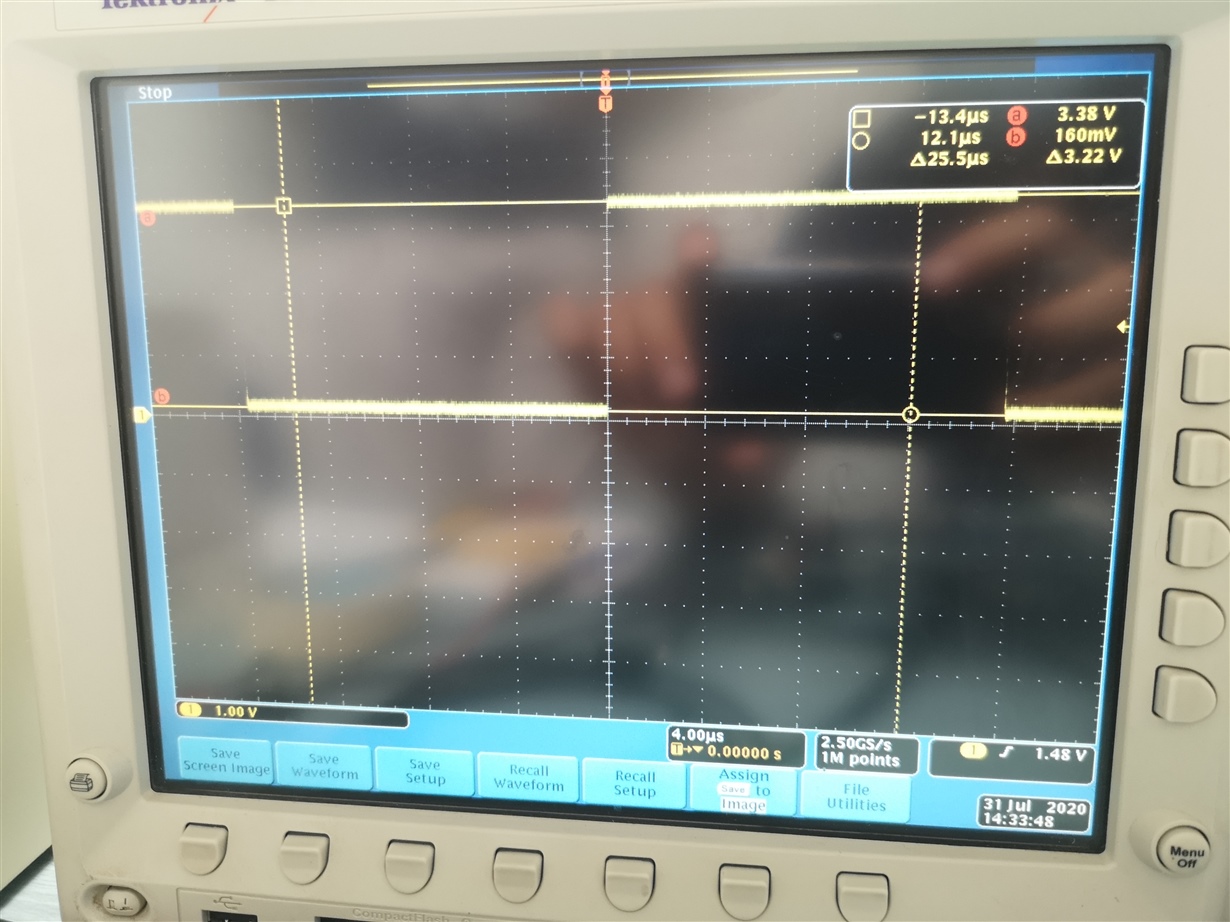

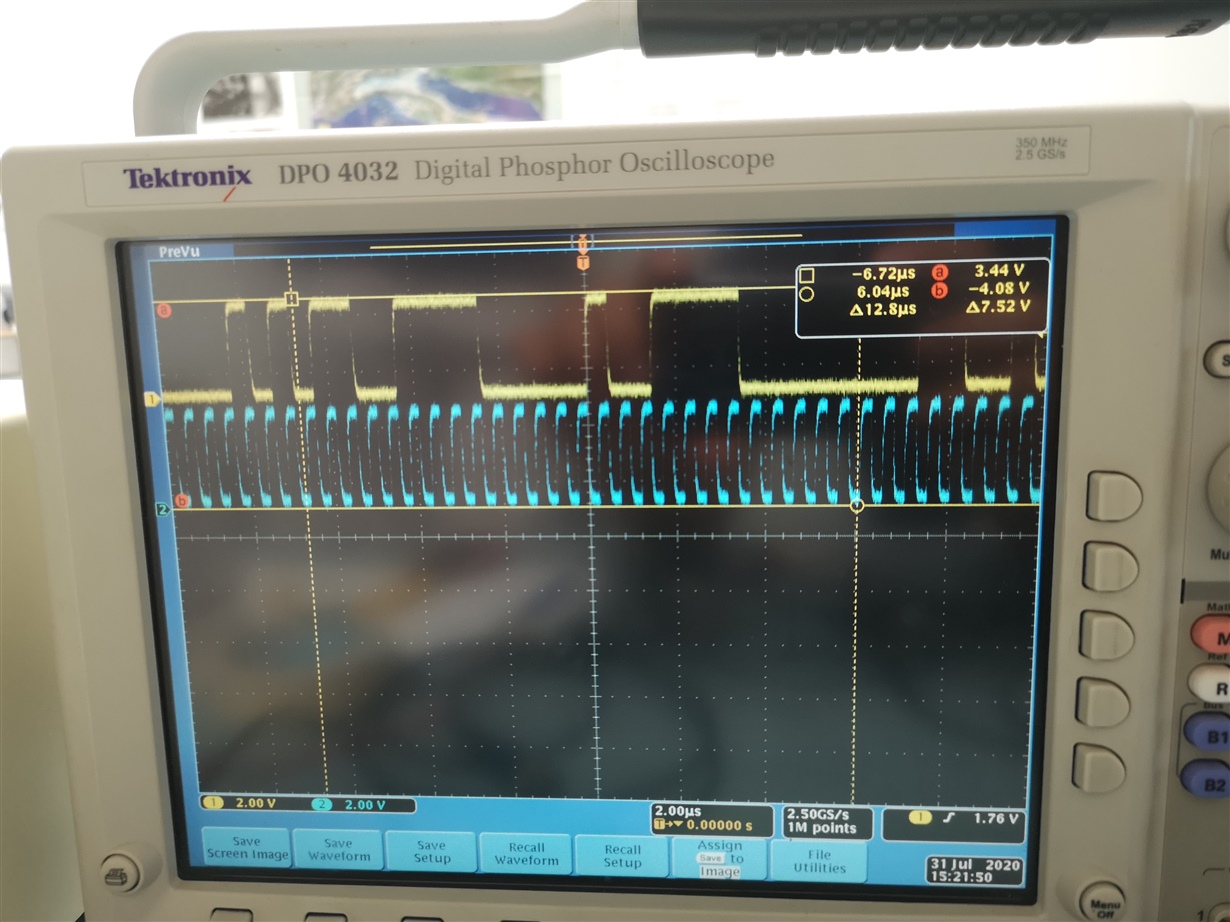

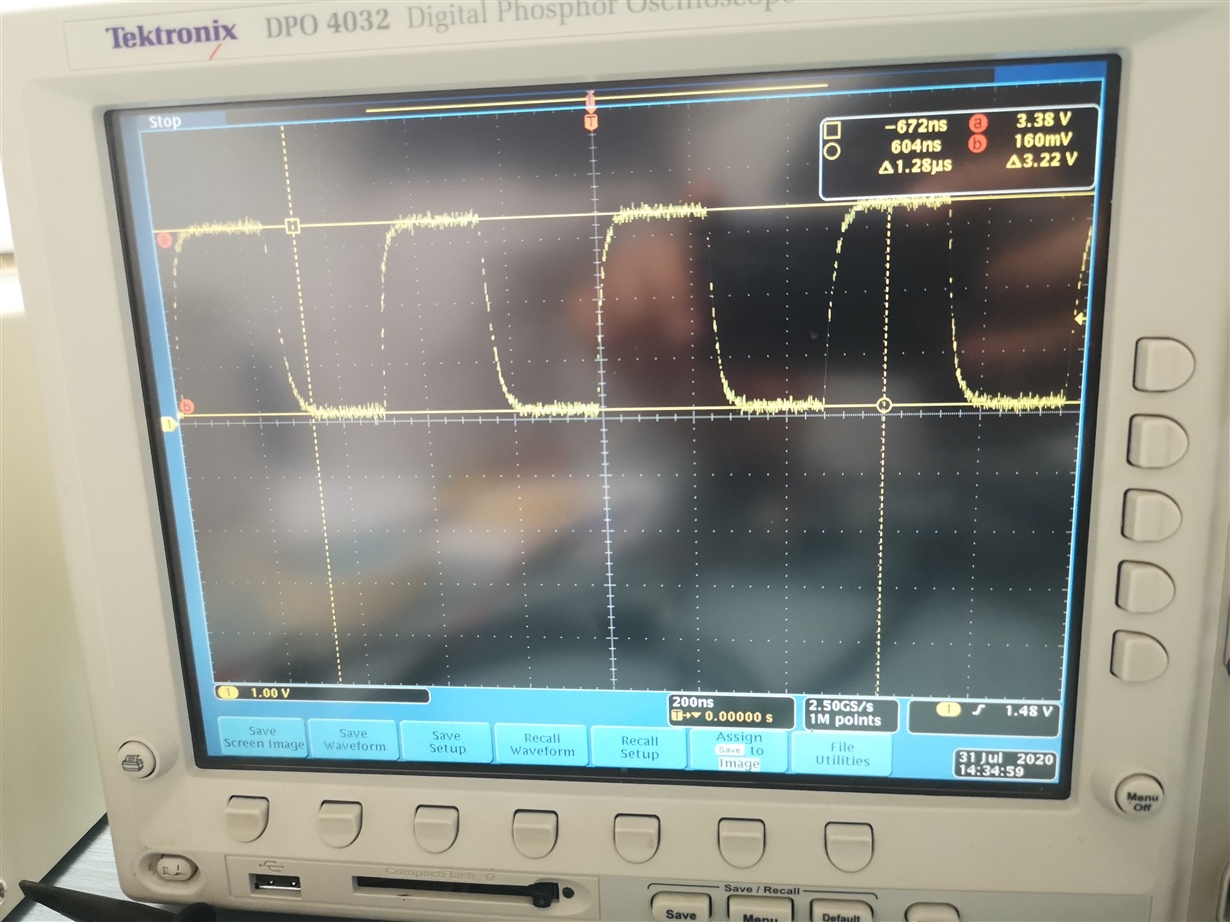

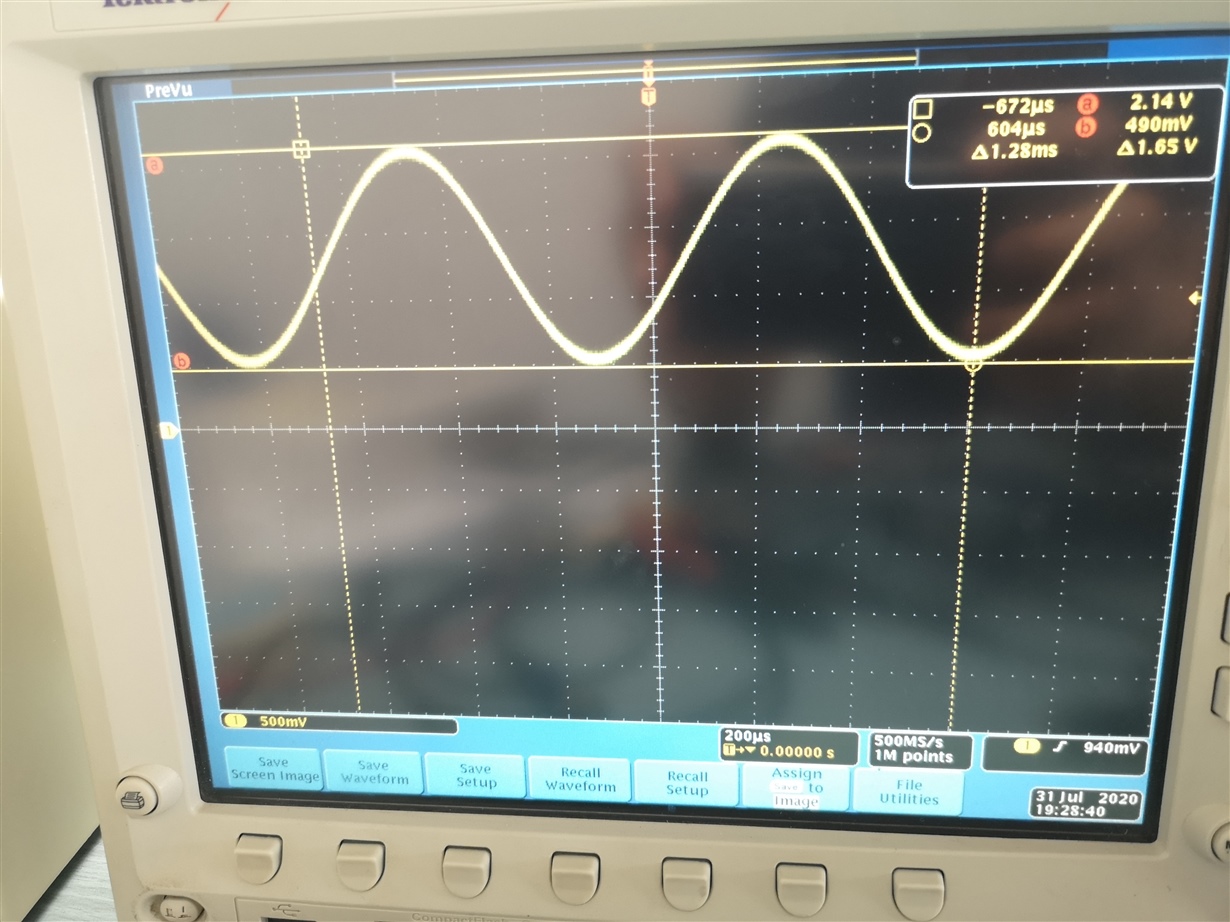

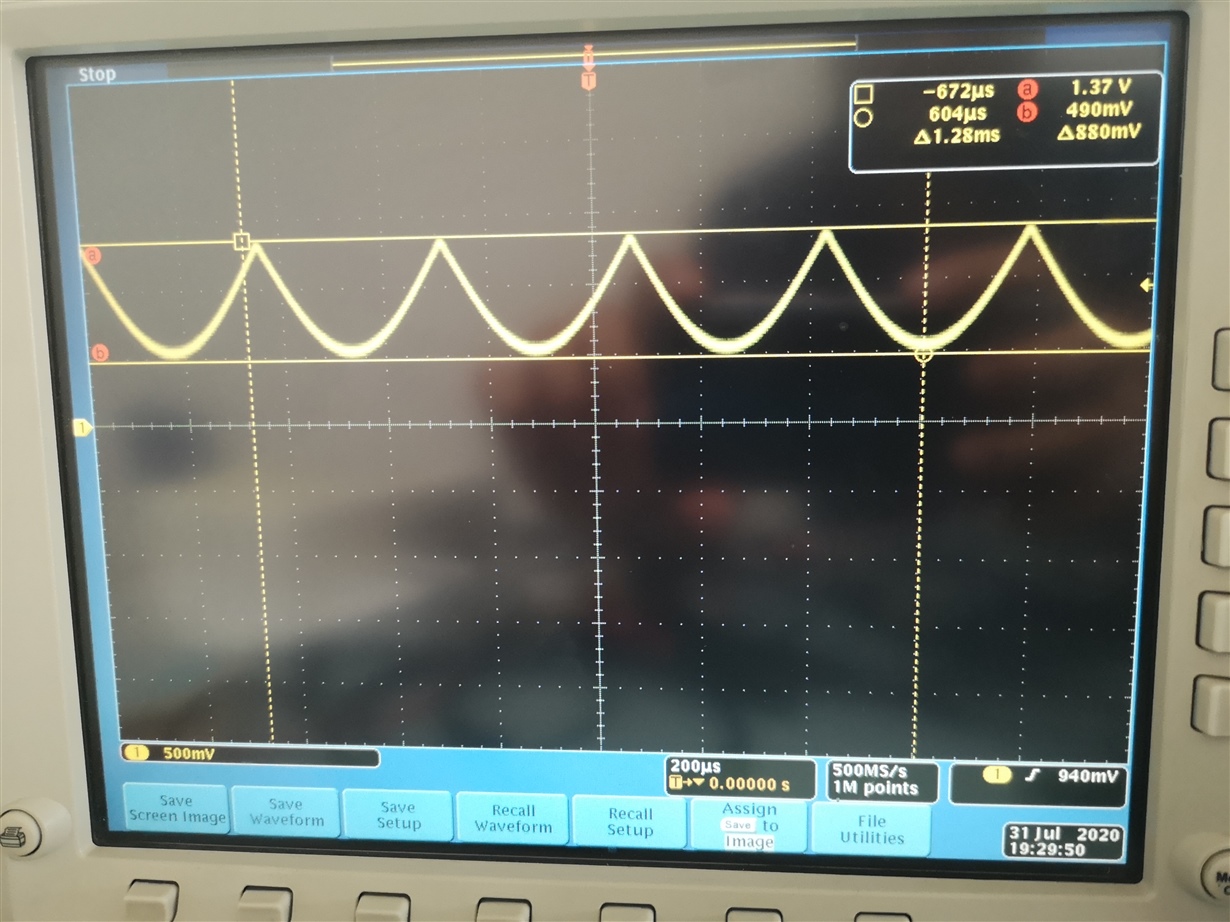

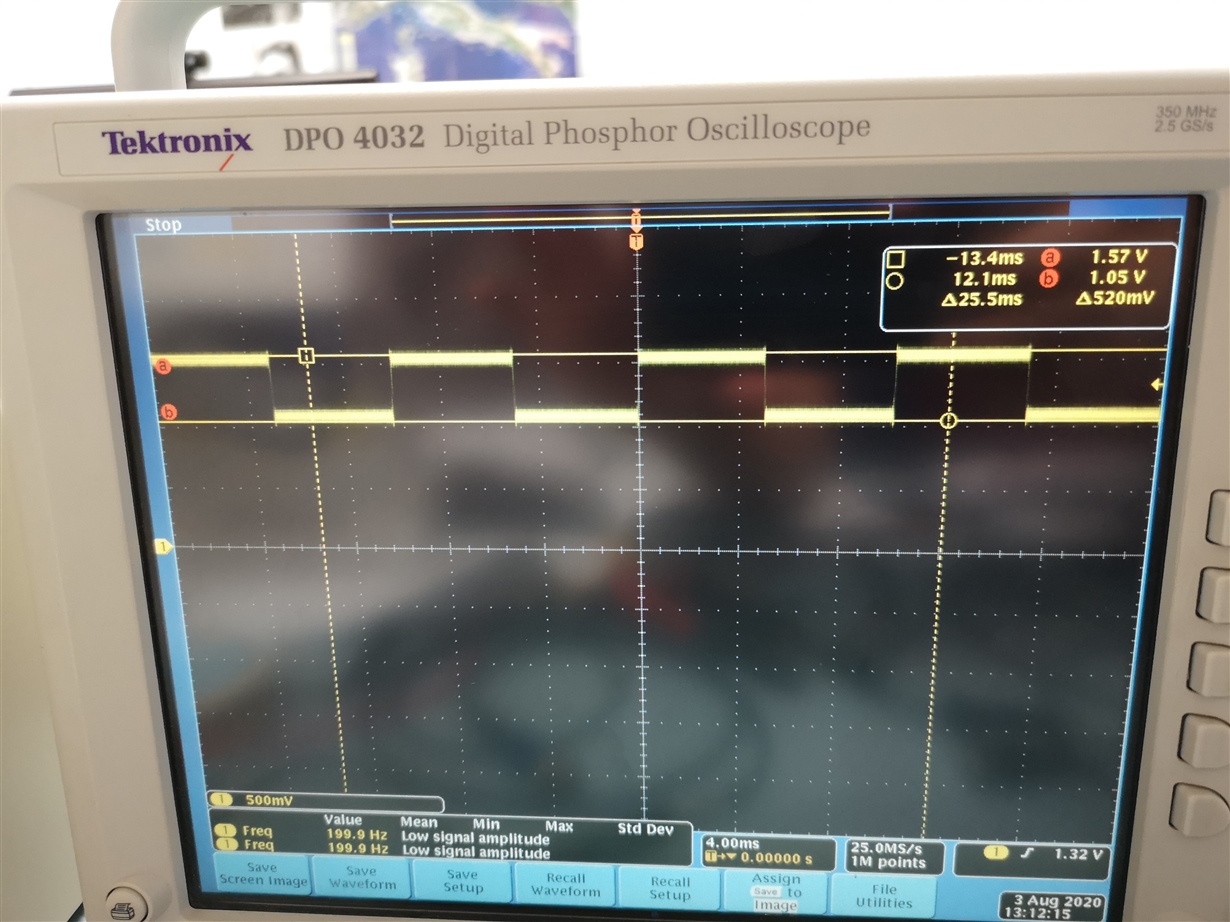

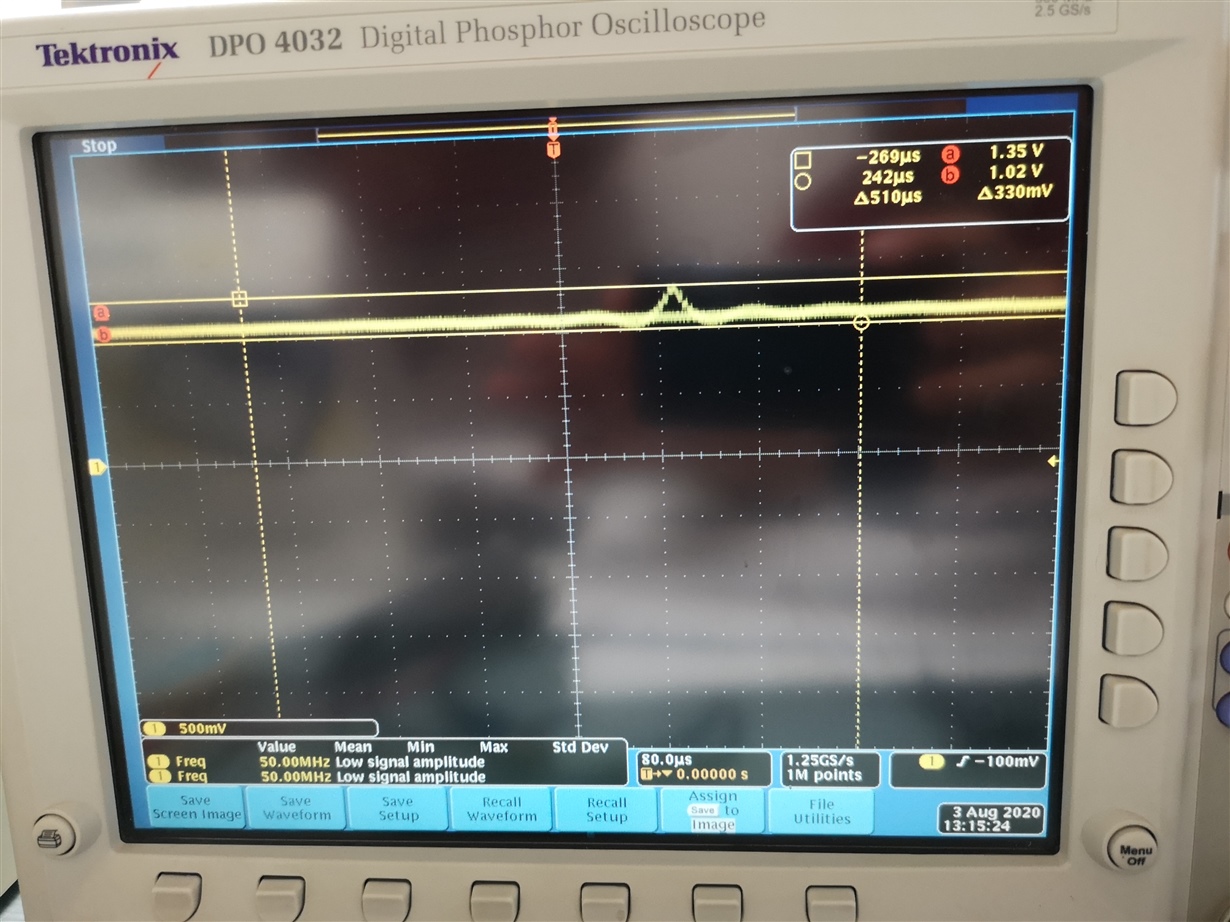

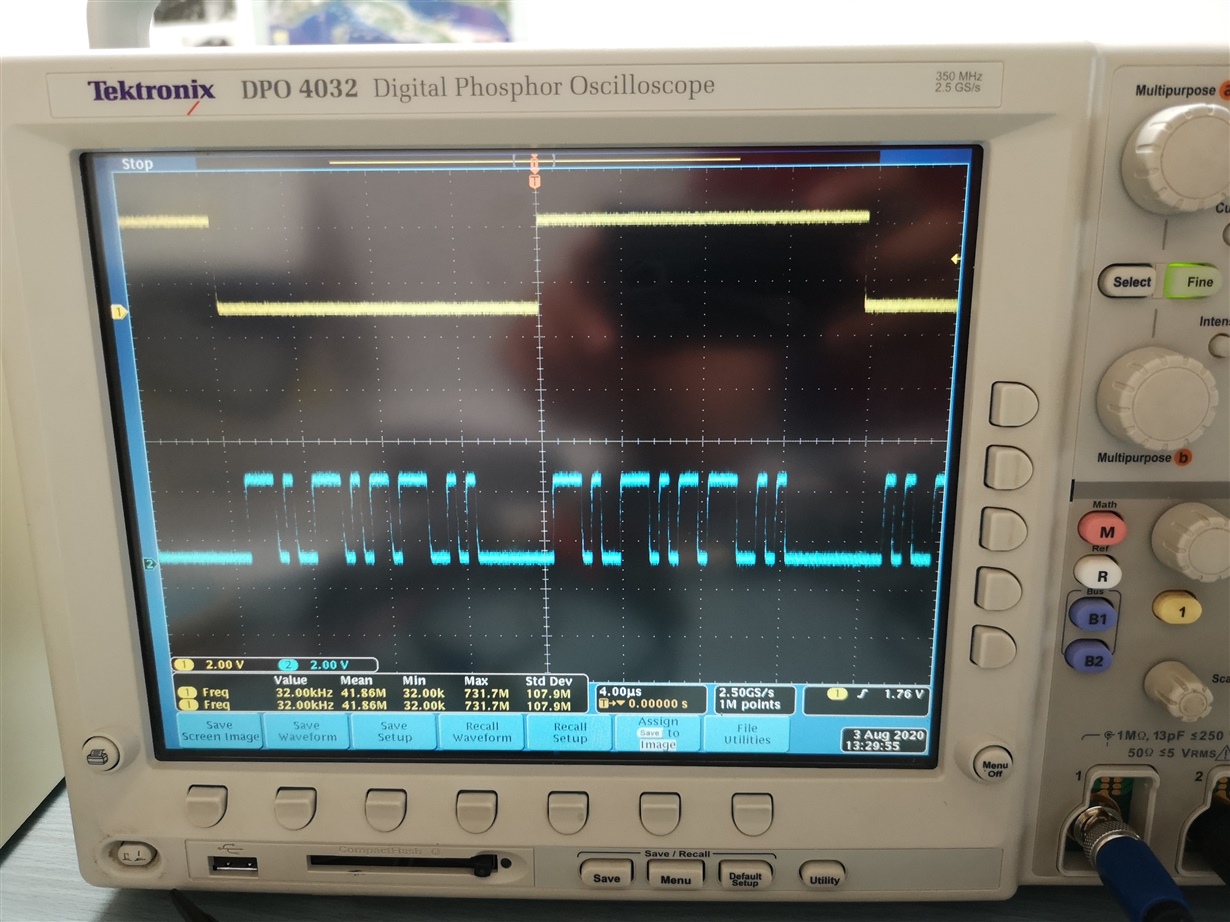

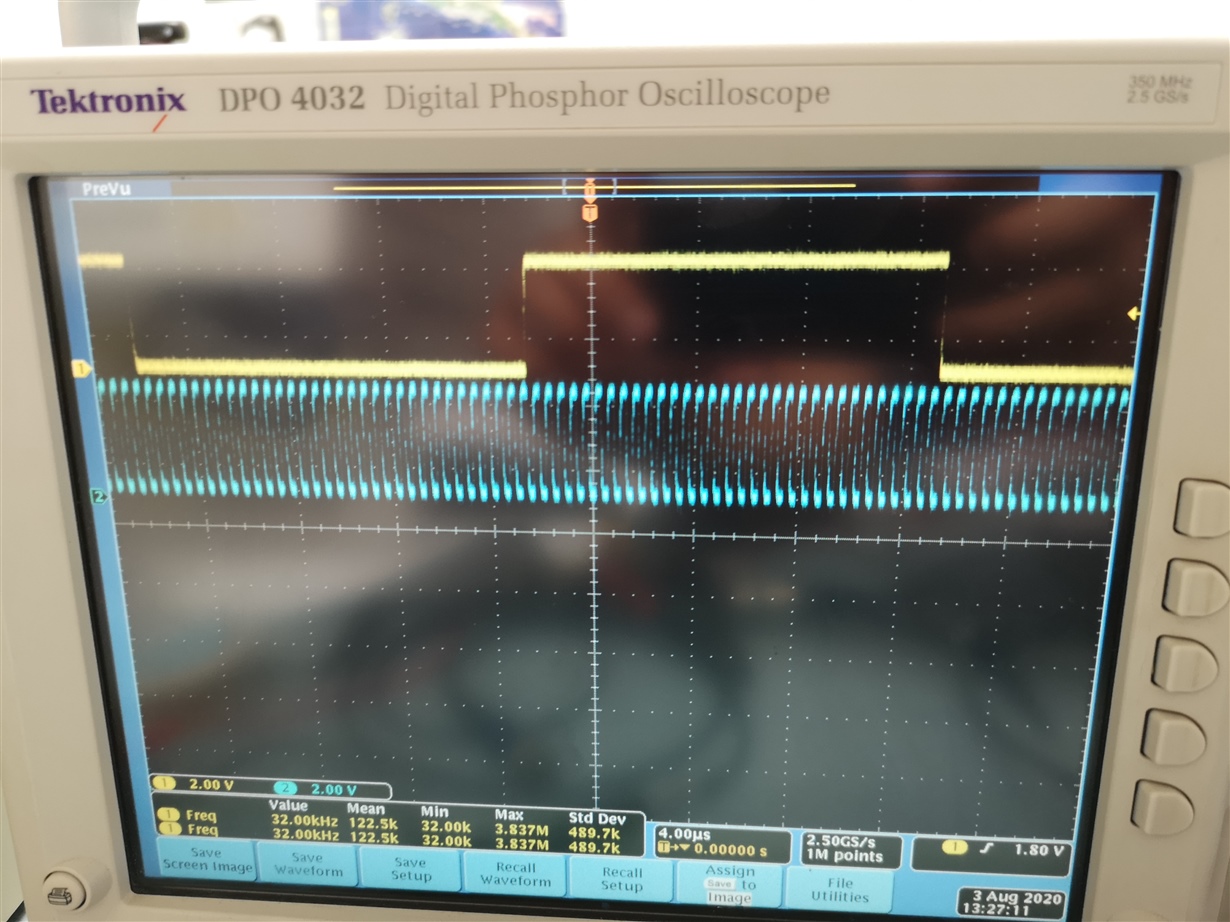

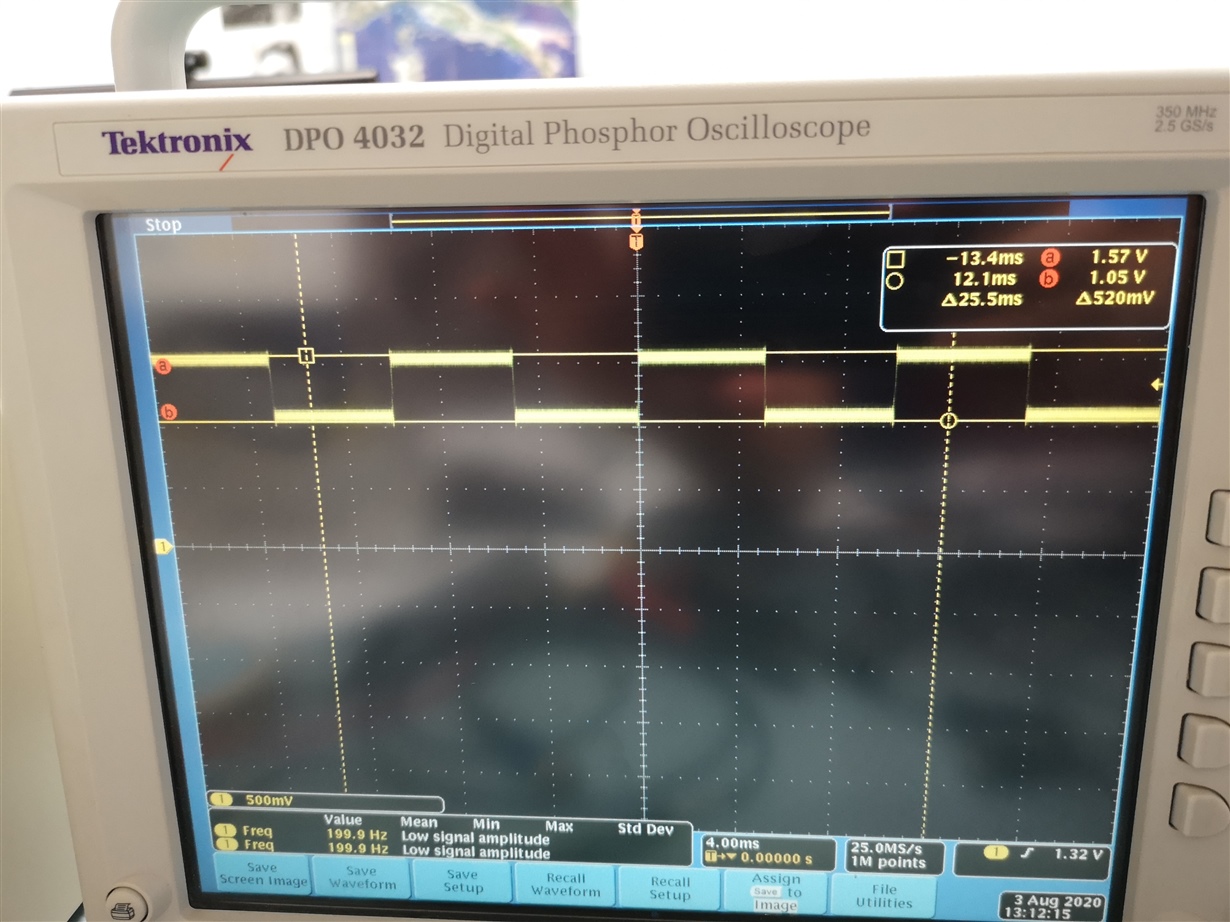

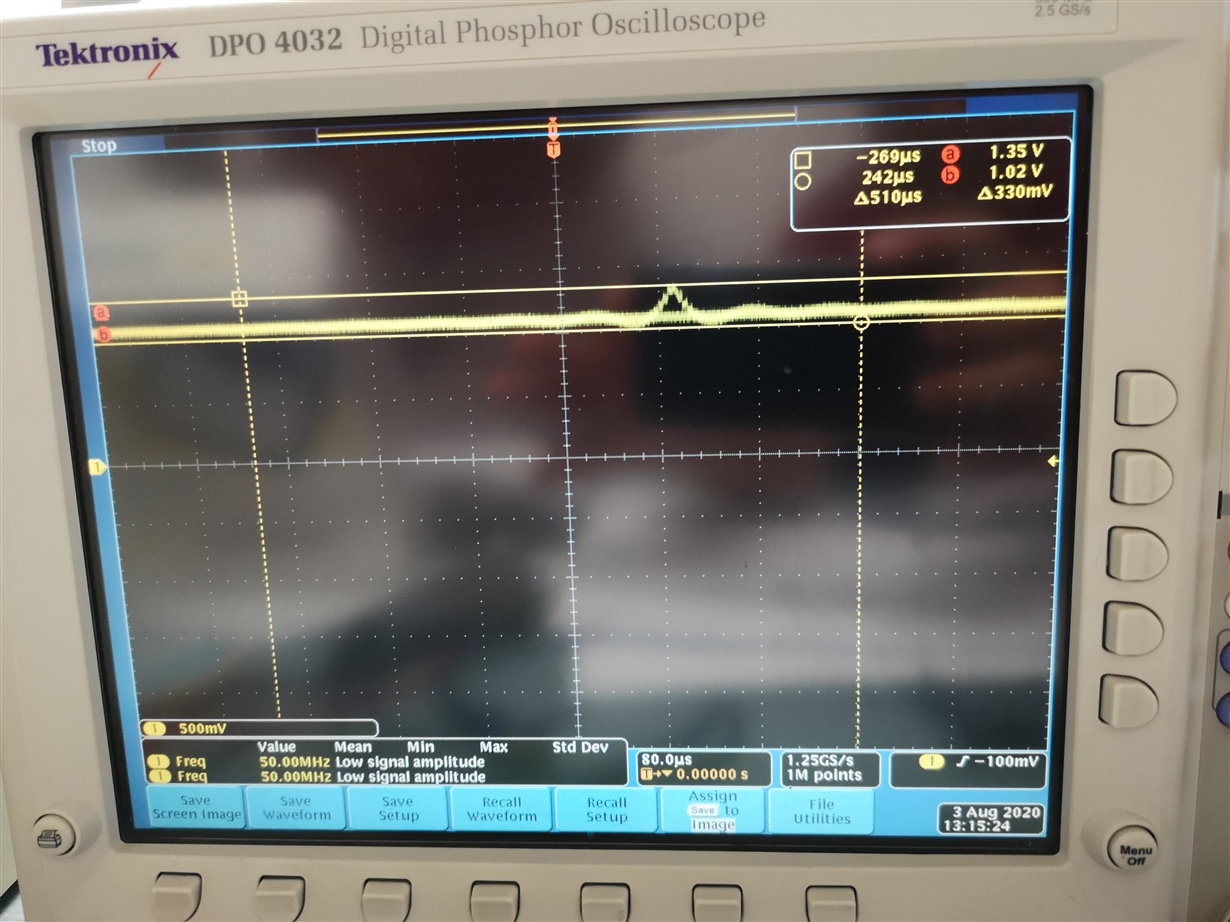

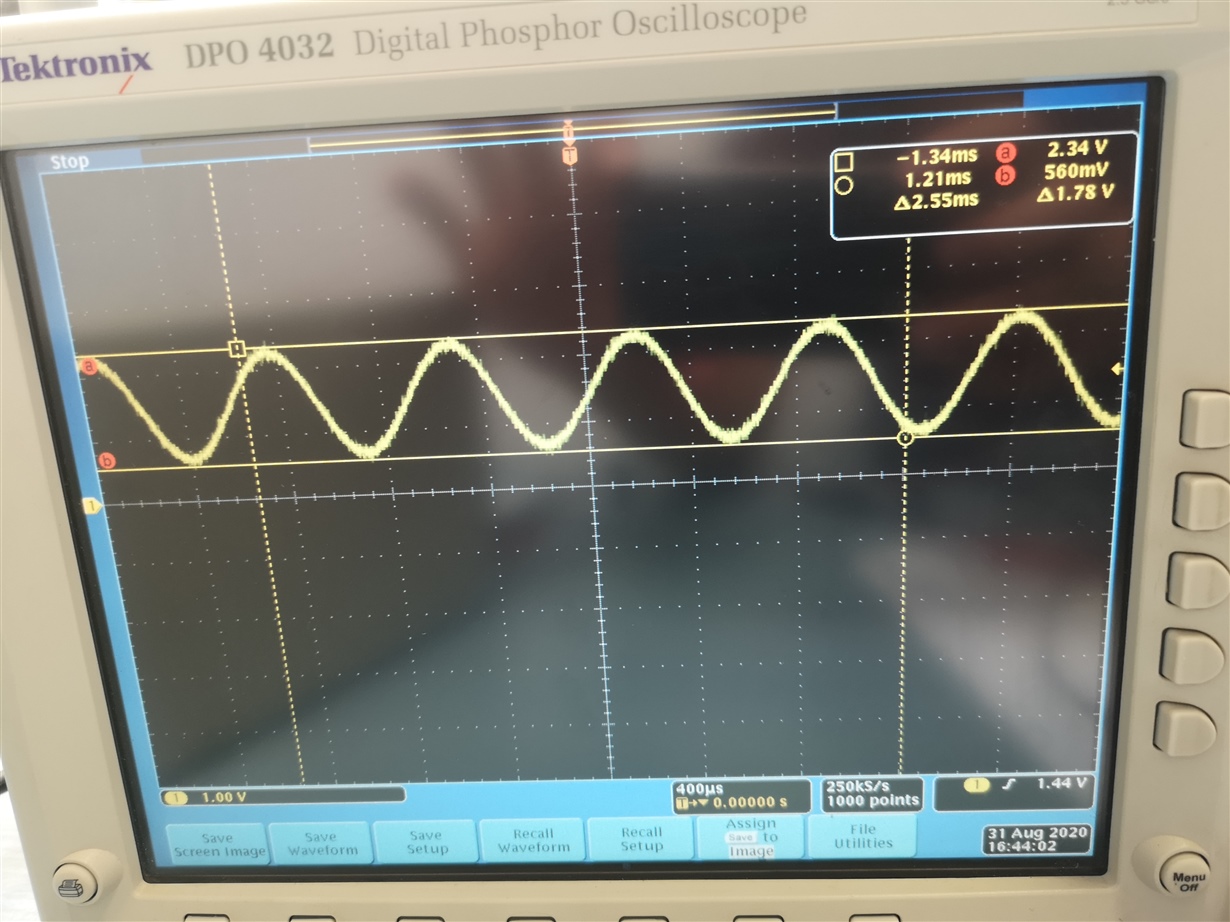

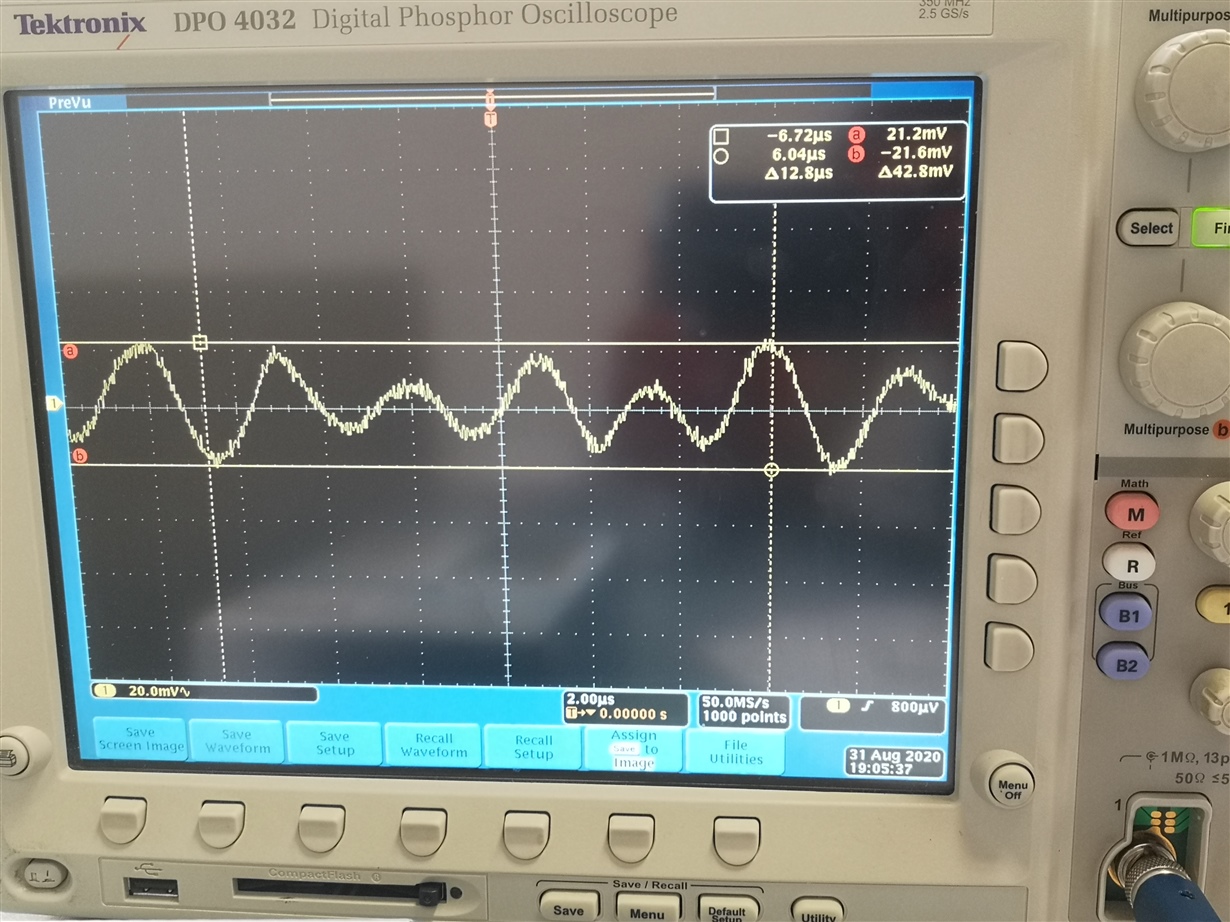

Hi, I need a DAC with AES/EBU input, so I used DIR9001 and PCM1793. The problem is that left signal from PCM1793 is not correct (is not a sine) . Could you please check the schematic below? Thanks in advance.