Hi team,

I would like to understand the theory of operation to optimize DRE performance of TLV320ADC6140.

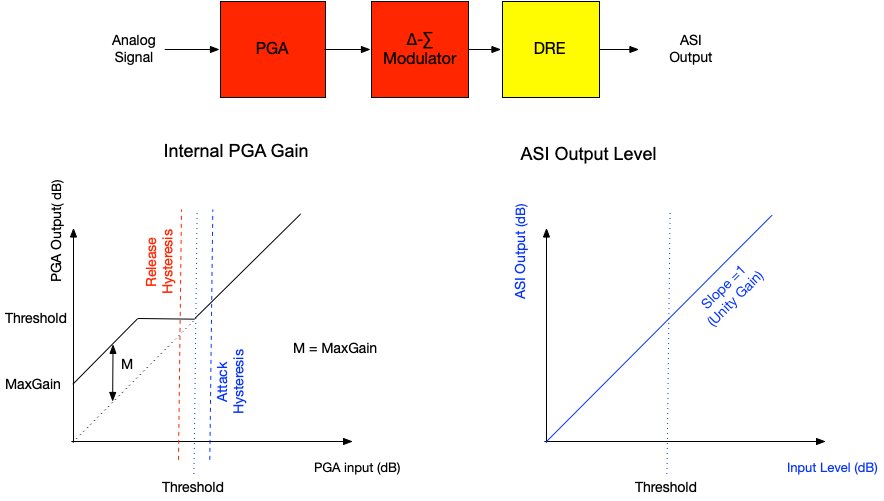

1. How does the "DRE maximum gain" setting affect the performance?

Could you give me a guide line to select the best setting?

2. How does DRE increase channel gain when the input level drops below DRE trigger threshold level?

It increases to DRE maximum gain, or it increases the channel gain linearly?

regards,