Hello,

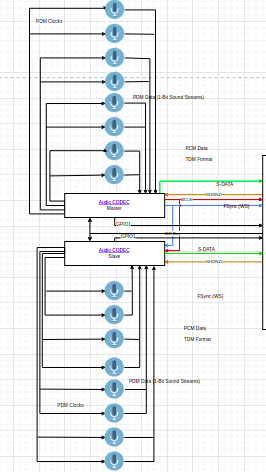

I am using a couple of tlv320adc3140 codecs with one as a master and the second as a slave, each codec is connected to 8 PDM mics with the 4 input pins, each pair is connected to one input pin.

the mics is arranged in a circle with 45 deg separated between each 2 pairs.

I managed to have a sound source between mics 1 and 8 and I was expecting that the wav channels of these mics should be synced as the distance between these mics and the source is almost the same.

The result was that there is a shift between them with almost 6 elements.

I am configuring the codec to work on rate of 48khz and I am getting the same difference (the 6 elements shift) when working on the 16khz rate.

I even used the CH8_CFG4 register to adjust this shift but the max value that I can set is 255 which corresponds to 2 sampling indices while I need 6.

I am looking for any help to figure out the root cause of this issue and how I can fix this shift.

please let me know if any more details is needed to clarify the issue.

Thanks in advance for your valued input.

Best regards,

Ahmed