Hi,please tell me.

I want to use TLV320AIC3101 and set the error to 0% at fs32kHz in master mode.

Is this right?

MCLK 12MHz

K=6.5536

R=5

P=6

fs=32kHz

12MHz*6.5536*5/(2048*6) = 32000 (error 0%)

Thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,please tell me.

I want to use TLV320AIC3101 and set the error to 0% at fs32kHz in master mode.

Is this right?

MCLK 12MHz

K=6.5536

R=5

P=6

fs=32kHz

12MHz*6.5536*5/(2048*6) = 32000 (error 0%)

Thank you.

Hello Kazuhide,

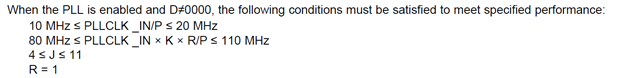

The PLL settings above will violate some PLL constraints when D ≠ 0000. Please see these constraints below:

I recommend using the PLL settings below. They are taken from the data sheet table 1:

P = 1

R = 1

J = 8

D = 1920

Using these PLL setting will generate an Fs(ref) = 48kHz. This is just a reference sample rate and in order to get an Fs of 32kHz, you will need to set Page 0, Register 2 to 0x11. This will divide 48khz/1.5 to get a 32kHz sample rate.

Regards,

Aaron Estrada

Hi Aaron,

Thank you for your reply.

I actually tried it and confirmed it.

Thank you.

Kazuhide Nagamoto

Hi Kazuhide,

Great to hear. I will now close this thread.

Regards,

Aaron Estrada