Other Parts Discussed in Thread: TPS22965,

Hi,

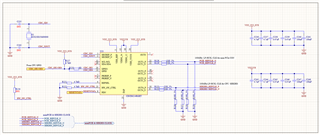

We use clock generator, CDCE6214RGET along with TI's CPU in one of our products. Could you please review our schematics?

Thank you.

Regards,

Kavin

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

The clock gen team has been out of office. Please expect a delay in response and thank you for your patience.

Kavin,

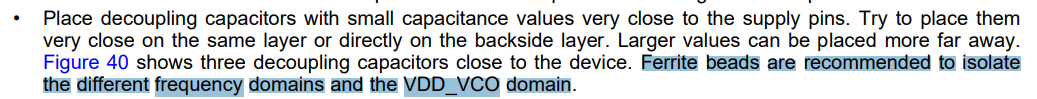

The VDD_VCO supply should be further isolated using ferrite beads [see image from datasheet]

Best,

Cris

Kavin,

Additionally, your SDA and SCL pins should be pulled to VCC, not left floating.

Best,

Cris

Hi Cris,

Thank you for reviewing our design.

We will update the schematics.

Regards,

Kavin

Sreenivasa,

Be sure to include a 1uF capacitor on the other side of the ferrite beads as well, if the supply does not already have it. Once that is done, your schematic looks good.

Best,

Cris

Hello Cris,

Great and thank you for the suggestions.

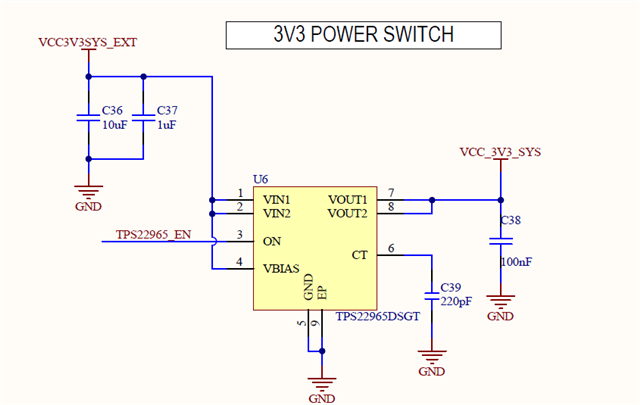

The Supply is switch by a load switch and has 1 10 uF + 1 uF at the input.

Regards,

Sreenivasa

Hello,

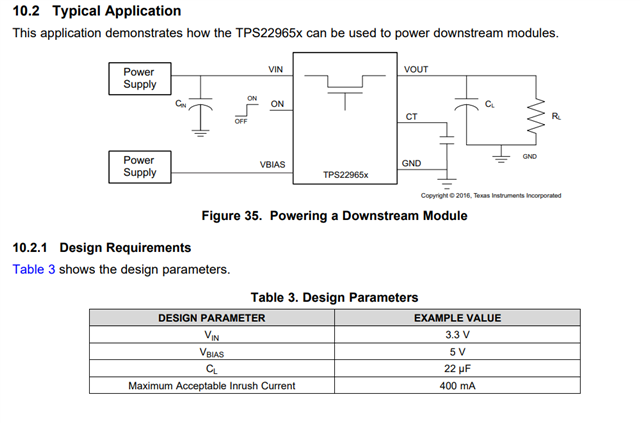

According to the datasheet of the TPS22965, the capacitor at Vout should be 22uF.

Best,

Cris

Hello Chris,

Thank you. Please refer below. Let me check with the eFuse team.

Regards,

Sreenivasa

Hello,

Apologies, I did not see that section. As far as the CDCE6214 is concerned, your 100nF capacitor on Vout should be fine.

Best,

Cris