Other Parts Discussed in Thread: DAC3283

Hi Ti Team

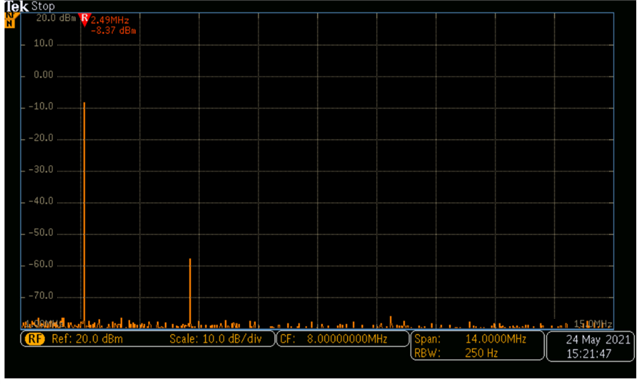

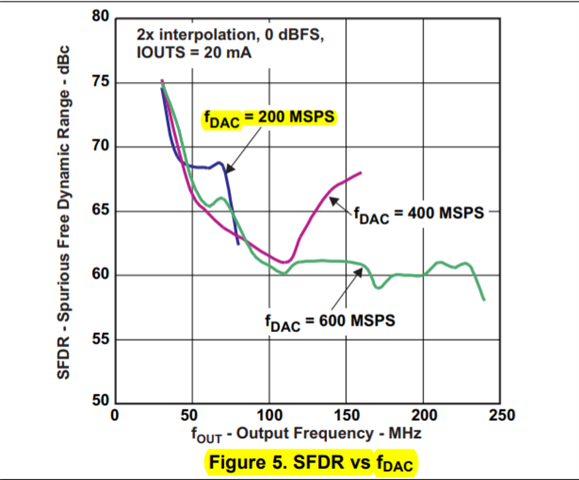

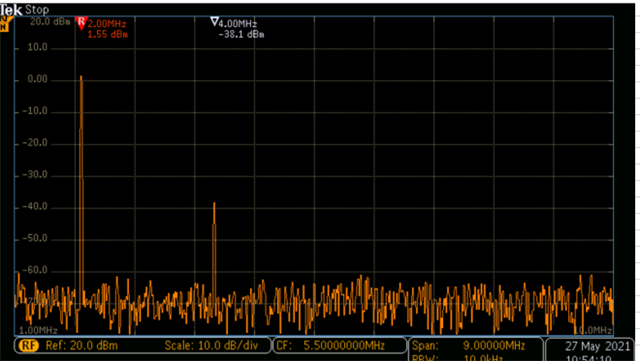

At the output of DAC3282, we are getting 2nd and third harmonics. These harmonics get amplification in our Transmitter chain as we are using amplifiers in the latter stage.

Our signal BW is from 500Khz - 20Mhz, DAC Sampling rate 210MSPS ( Using x2 Interpolation). DAC gain is X66. In a later stage, we are using LPF cutoff 28Mhz.

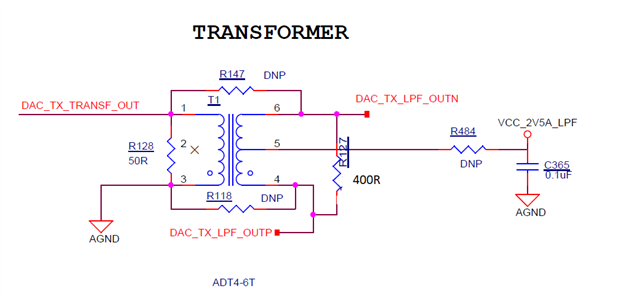

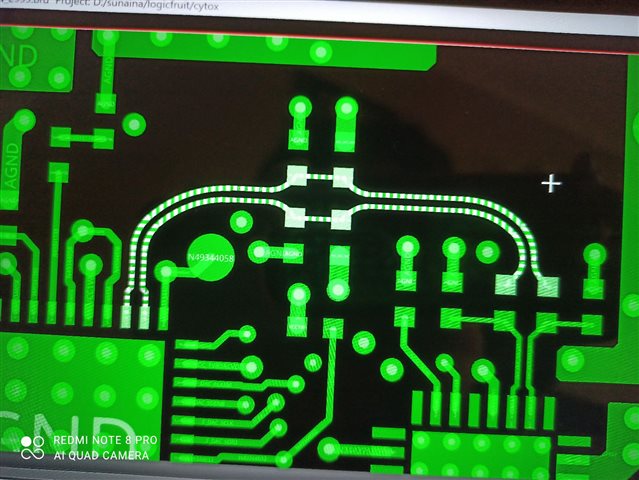

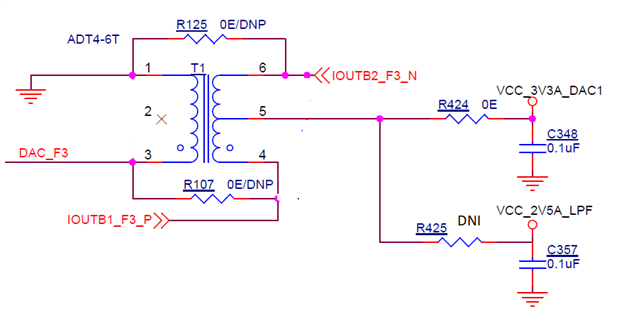

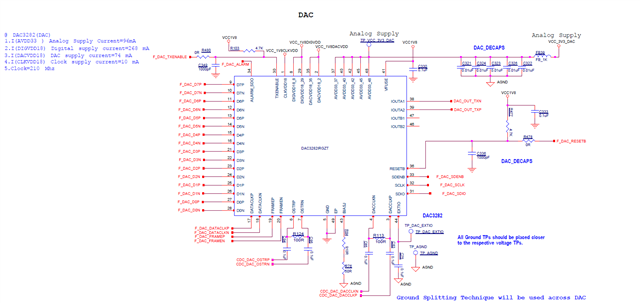

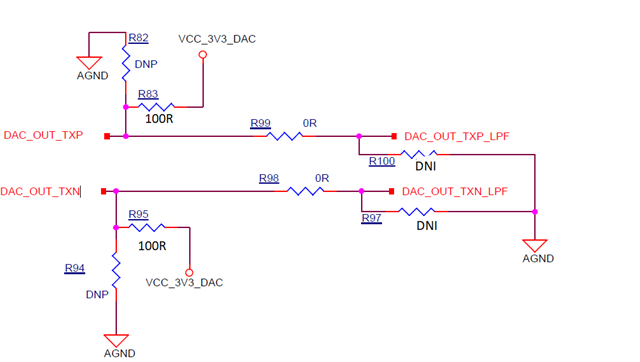

PFB Schematics of DAC3282 and DAC front-end circuitry. DAC CLK is LVPECL 210Mhz.

Please suggest review points to fix this issue as earliest.

Regards

Balvan Singh