Hi team,

We got inquires from customer as following.

- Duty cycle of CLK

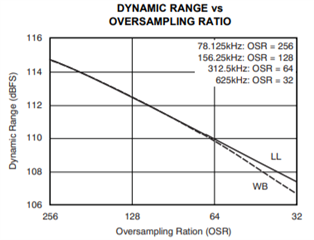

In case of multiple conversion, customer will configure ADS1672 CLK = 20MHz, FastResponse, LowLatency, DR=625ksps.

According to the datasheet, the duty cycle of CLK should be very close to 50% while min, max shows 45% and 55% in timing requirements.

Is it enough min 45% and 55% ? If no, could share the target number ? - The target number for clock jitter

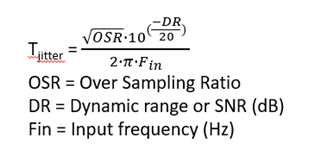

In case of configuration CLK=20MHz, FastResponse, LowLatency, DR=625ksps and maximized SNR between 600Hz and 60kHz, customer would like to know the target number of clock jitter.

Or it would helpful if we can share the figure such as Figure 2. SNR plots for oversampling ADCs(a) or the data such as table 1. which shows between clock jitter, SNR and frequency. Could you share the such data for clock jitter ? Customer is worried about the degrading SNR performance by increasing jitter.

Thank you and best regards,

Michiaki