Other Parts Discussed in Thread: DAC63004, , ENERGIA, DAC53204, ADS7953

Hi,

I want to "marry" DAC with NVM and multi-channel ADC on one SPI interface.

For this one of them should respond on first data package (? bit) and other should ignore it and respond to last data package (may be of different length) during the same /CS. If I will find devices, working this way, everything should work well. Today I have such an arrangement with not TI parts and with no NVM in DAC. SAR ADC locks first 8-bit and responds immediately (during the same /CS) with result, and DAC waits until the end (rising) of /CS and takes last packet before that as a command (even with NOP option).

I also need that ADC and DAC will be in complete silent mode during inactive /CS.

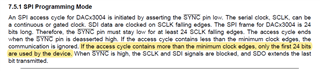

Now, with new DAC devices, with NVM inside, I would like to upgrade functionality and get the similar performance, but those DAC-s are responding to the first x-bits after the /CS was applied and it ruins me all fun :-).

This is from DAC63204/DAC63004 data sheet, page 27: "If the access cycle contains more than the minimum clock edges, only the first 24 bits are used by the device."

Need advise, please.

.

.