If our design condition is 2MHz, how is the SPI interface timing specification defined? Is it 500ns (1/2MHz)?

If so, will the time between Tden_CSDO and Tdz_CSDO exceed 500ns, will it cause any impact?

BR, Gary

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

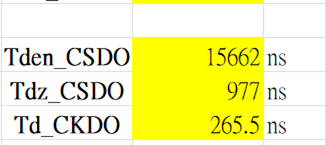

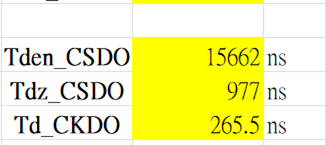

If our design condition is 2MHz, how is the SPI interface timing specification defined? Is it 500ns (1/2MHz)?

If so, will the time between Tden_CSDO and Tdz_CSDO exceed 500ns, will it cause any impact?

BR, Gary

Hello,

With a clock frequency of 2MHz, which is equivalent to 500ns.

the conversion time is a fixed value, it will always take 600ns (or 192 in turbo mode)

the three timing parameters you have mentioned are also fixed values, these do not scale, and are controlled by the device. These three parameters provide information for the end user to anticipate when data on SDO will be available to read, using CS and SCLK as references

Perhaps I am not understanding your concern, would you explain?

Regards

Cynthia