Hello,

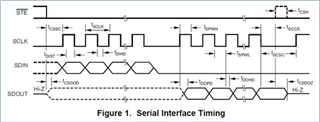

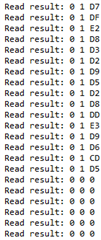

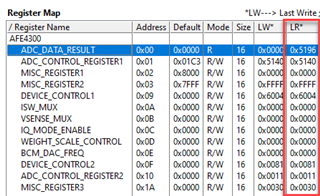

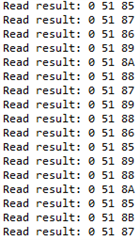

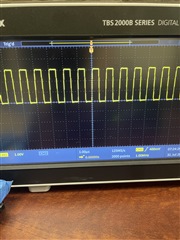

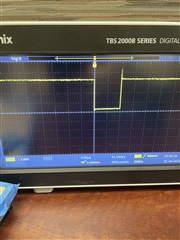

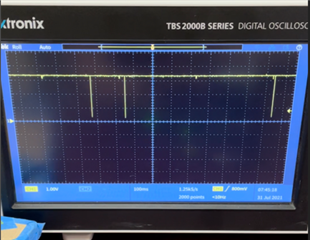

I am trying to connect an AFE4300EVM to a nRF5284-DK using the evaluation module's SPI interface. By detaching the MMB3 board from the AFE4300EVM and wiring the pins of J103 to the correct GPIOs of the nRF52840 development kit, I can connect the two boards together. I am able to write to the AFE4300's registers, which was tested by checking the voltage of VLDO after enabling the weight scale chain. However, I'm facing an issue when trying to read from any of the registers, including ADC_DATA_REGISTER. The RDY signals begins in a high state, pulses low for 8 microseconds as each register is written to, and finally remains high / does not interrupt after writing to the registers.

My questions are:

1) Why does the RDY signal begin high, while Figures 10 and 11 of the datasheet indicate that RDY should start low?

2) Should I be monitoring the RDY signal while writing to the registers or only while reading?

3) If RDY's brief low pulse signifies the end of a conversion, should I be prepared to immediately read the data after the last register write, or can I prevent the interrupt/data conversion from occurring right away?

4) Does STE serve any purpose if the AFE4300 is the only slave device on the serial bus?