Hi,

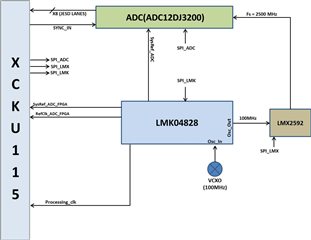

I am using ADC12DJ3200 which is interfaced with Kintex Ultrascale FPGA.

ADC operated in JMODE 5 and K = 32.

What are the configuration steps for ADC?

On power on after configuring LMK,LMX and ADC the sync is stable, JESD link is up. I am finding ADC loses its sync after sometime and JESD link is down.

My sampling rate is 2.5GSPS. Sysref is 19.53125MHz and it is continuous.

Is it related to sysref calibration sequence?

Sysref position capture is showing as below.

2C = 0x8D

2D = 0x61

2E = 0x8C

When it goes out of sync Realigned Alarm bit is set in Alarm Status Register.

What is causing ADC to lose it sync?