Hi Team,

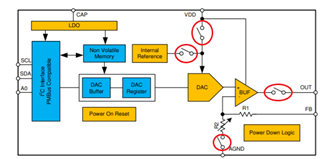

In the following figure, I can see 4 internal switches at VDD, REF, OUT and AGND.

My customer has a two questions regarding the internal switches.

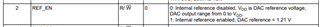

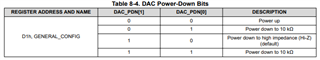

1. Is it able to set the initial ON/OFF state for these switches by setting EEPROM? The Initial state means the state just after the POR. I understand the initial state of switches conncted to VDD and REF can be set by REF_EN bit at D1h. But, how about the switches at OUT and AGND?

2. Could you tell me the timing that the switch state is set after POR?

Regards,

Saito

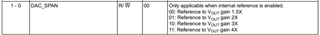

The variable resistor R2 determines the reference gain setting. This is set by the DAC_SPAN bits in the GENERAL_CONFIG Register.

The variable resistor R2 determines the reference gain setting. This is set by the DAC_SPAN bits in the GENERAL_CONFIG Register.  These can all be saved in the EEPROM

These can all be saved in the EEPROM