1. Use the environment

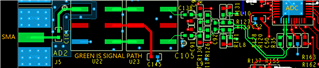

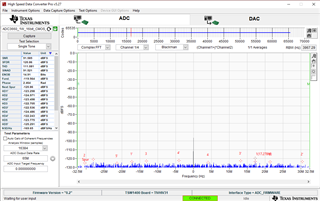

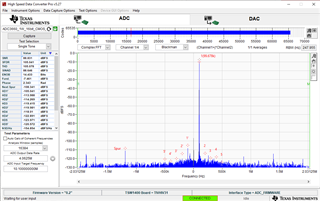

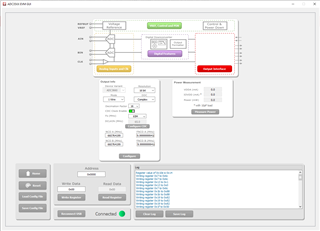

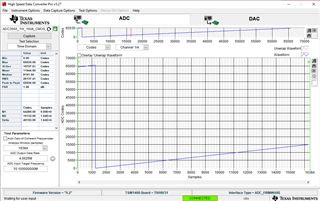

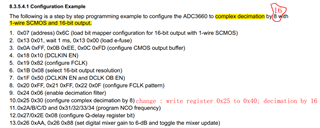

The ADC3660 is configured with 1Wire, 16bit, FS=65MHz, DCCLKIN=65MHz, 16 complex Decimation

2. problems

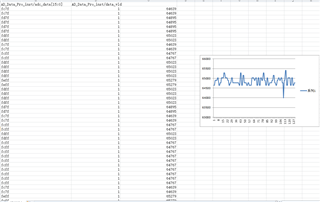

External to the ADC a sinusoidal signal, ADC acquisition result is basically unchanged, is a constant value.When the board is not powered on, use an oscilloscope to test PIN 38 39, that is, BINP BINM input signal is OK.After the board is powered on, the input signal is drowned by noise.