Other Parts Discussed in Thread: ADS8588S

Hi Team,

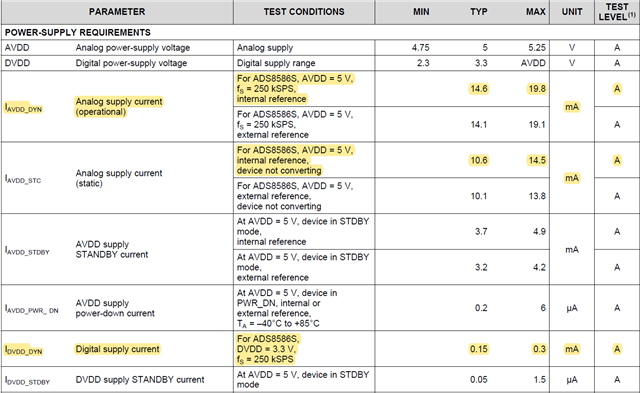

I developing a board for my project which uses ADS8586S. I am planning to sample the analog inputs at 10ksps and send the data via SPI to CC3220 at 250kHz. Is it possible to have different rates for input sampling and data throughput? Also I am sampling 6 channels simultaneously. So how do calculate the power requirement from the given electrical characteristics.

It is given that Analog supply current 14.6mA at 250ksps. If I am calculating for worst case scenario I need to consider 19.8mA maximum current for my calculation right?. Since I am sampling simultaneously do I need to consider this 19.8mA for each channel?

Same goes for Digital output for SPI communication since I am using three pins for my SPI, should I consider 0.3mA maximum current for 3 lines for my calculation?

My sample calculation is as follows.

AVDD = 5V

DVDD = 3.3V

IAVDD = 19.6mA

IDVDD = 0.3mA

sampling 6 channels simultaneously and SPI communication is working at 250kHz. Then,

Total Power consumed = ( 5*19.8mA*6 ) + ( 0.3*3.3 ) = 595mW

Is this calculation correct?

Since I am using a AC/DC converter instead of battery, I am calculating for maximum power requirement to choose my converter and LDO. Or should I need to account for static and power down conditions ?

Regards,

Vineeth