Other Parts Discussed in Thread: DAC39J82, , DAC38J84EVM, DAC38J84

- We considered FMC_SEN_DAC and FMC_SEN_LMK as active low signals which we have connected to a multiplexer and operating either LMK or DAC with the help of a select line .

- Query : Can you please tell us the active level of these signals?

- Taking reference from schematic, we are configured the direction of pins as follows, please confirm whether the directions are fine.

- FMC_SDIO => Output from FPGA and Input to EVM(connected to CPLD).

- FMC_SDO => Output from EVM and Input to FPGA.

- FMC_B5 => Output from EVM(DAC) and Input to FPGA.

- FMC_B6 => Output from EVM(LMK) and Input to FPGA.

- FMC_SDIO => Output from FPGA and Input to EVM.

- FMC_SDO => Output from EVM and Input to FPGA.

- Query : Please tell which signals we should use for SDIO and SDO for bring up. Also please mention the functionality of all the pins mentioned above.

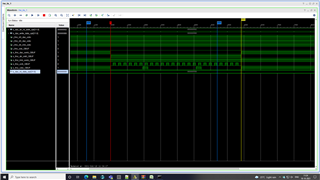

- We are currently using the SCLK frequency as 6.25 MHz.

- Query : Is this okay to use or should we need to reduce even more. As per the data sheet it was mentioned to use maximum of 20 MHz.

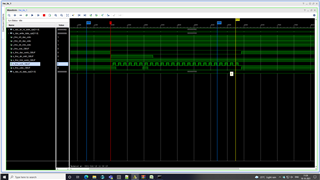

- As per the DAC_39J82 datasheet it was mentioned that SPI interface was three wired by default, and to make it four wired it was suggested to make 7th bit(sif4_ena) of config2 register high.

- Query : We are currently using 4 wired SPI controller; can you please confirm whether will it work by writing the 7th bit of config2 register high.

- Query : Can the 4 wire SPI controller be used from the start ?