Other Parts Discussed in Thread: ADS131A04, INA849, ADS127L11

Hello,

I have problems getting ADC to work correctly. I am sending configuration over SPI, then PWM 50% on START line.

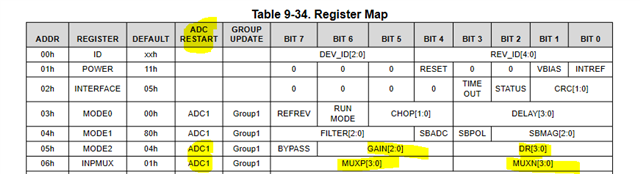

With START 20Hz, I am getting DRDY signal, but when issuing data read command, I get 0x00000000. Non-inverting input is scanning input lines, currently unloaded. Inverting input is connected to 50% Vref (internal reference).

With START 10kHz (and DR register 0xE), ADC gets silent after receiving configuration.

Is my part dead? Or wrong config / transmission sequence?

My goal is to achieve 1kSPS/10ch with as little noise as possible. I will then connect instrumentation amplifiers to non-inv inputs (I need higher gain than internal PGA). Primary sources of signal are load cells.

Thanks in advance,

Stanislav

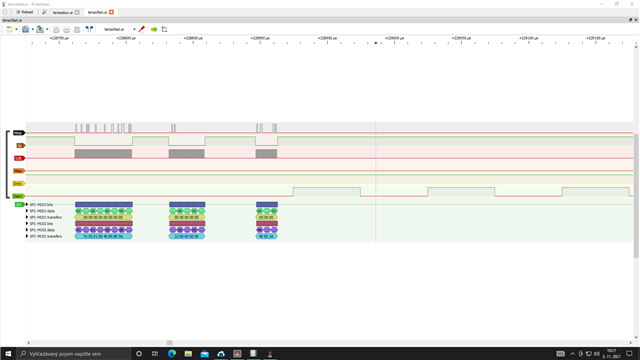

Setup sequence with fast START signal - after this nothing happens.

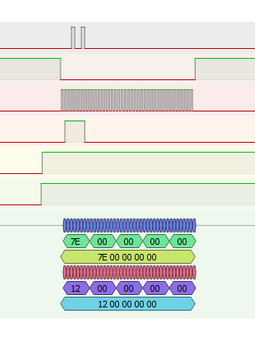

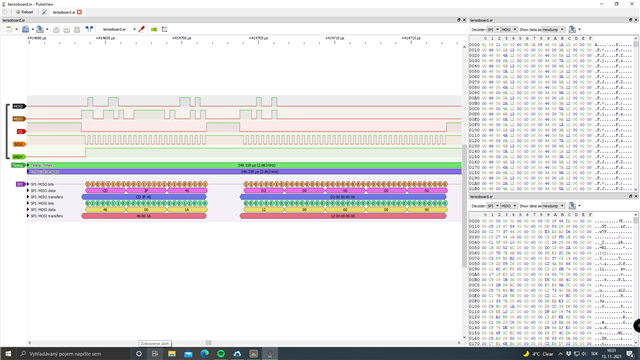

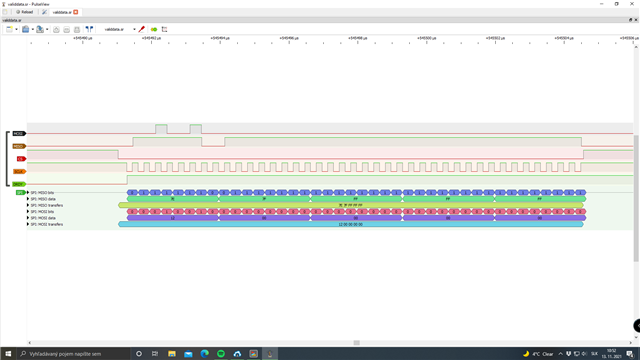

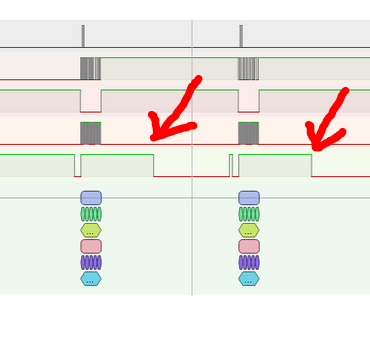

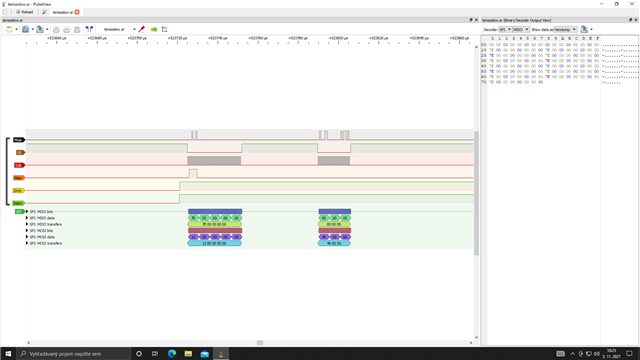

RDATA + WREG INPMUX with slow START signal. Also dump of communication at MISO line.

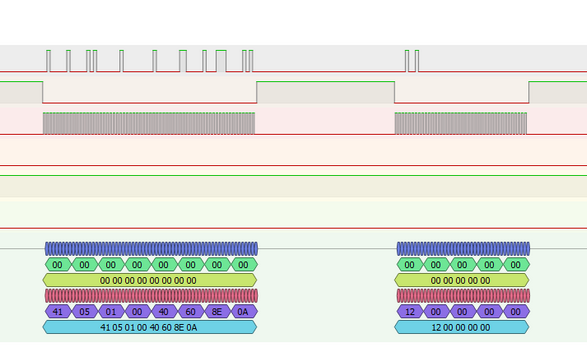

Setup sequence with slow START signal. Also dump of communication at MOSI line.

With slow START signal, there are continuous conversions.