Other Parts Discussed in Thread: LMK04828,

Hi,

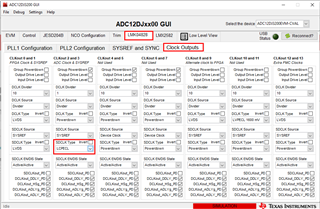

i configured my ADC12DJ3200 as follows:

0x0000 0xB0 // Do soft reset

delay for 100ms

0x0200 0x00 // Clear JESD_EN (always before CAL_EN)

0x0061 0x00 // Clear CAL_EN (always after JESD_EN)

0x0201 0x00 // Set JMODE0

0x0202 0x03 // Set KM1=3 so K=4

0x0204 0x05 // Use TMSTP+/- input, offset binary data, scrambler enabled

0x0205 0x04 // Ramp test mode

0x003B 0x03 // Enable TMSTP Rec and TMSTP LVPECL

0x0213 0x07 // Enable overrange, set overrange holdoff to max period 8*2^7 = 1024 samples

0x0048 0x03 // Set serializer pre-emphasis to 3

0x029 0x30 // enable the SYSREF receiver circuit and Set zoom bit

read 0x02C-0x2E

0x029 0x74 // set SYSREF_PROC_EN and SYSREF_SEL

0x0061 0x01 // Set CAL_EN (always before JESD_EN)

0x0200 0x01 // Set JESD_EN (always after CAL_EN)

0x006C 0x00 // Set CAL_SOFT_TRIG low to reset calibration state machine

0x006C 0x01 // Set CAL_SOFT_TRIG high to enable calibration

After set the master_reset_n signal to ‘1’ and Set the rx_sync_reset_vio signal to ‘0’ in the Reference Design following values are in the Registers 0x0208 and 0x02C1:

0x0208 = 0x0C

0x02C1 = 0x08

So it seems the JESD204 link isn't established

Do you have any advice for me ?

BR

Chris